# ECONOROM 2708

# **ABOUT ECONOROM 2708**

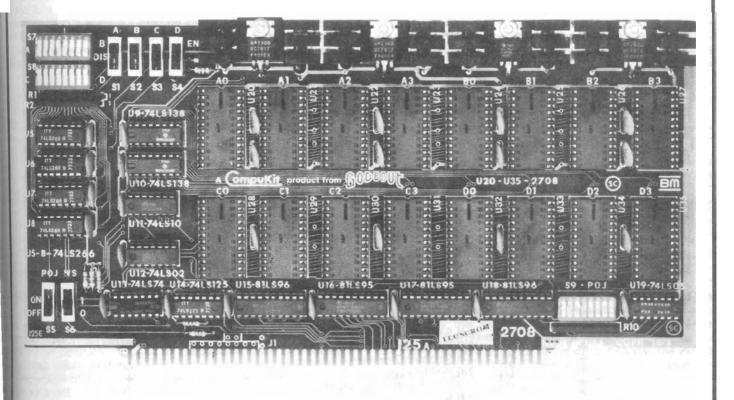

Congratulations on your decision to purchase ECONOROM 2708, a 16K x 8 EPROM board designed specifically for electrical and mechanical compatibility with the proposed IEEE S-100 buss standard. The S-100 buss currently is one of the most popular in the industry and by far the most prolific; we believe this board, with the rest of the S-100 portion of the COMPUKIT family is one of the best memory boards available for that buss.

We recommend that the parts in this kit be checked against the parts list for completeness and that these instructions be read through carefully before starting. Assembly should take from one to four hours, depending on previous experience. Upon completion, you will discover as thousands of satisfied COMPUKIT memory owners have discovered, the pleasure of using a fine memory board that just works and works.

As the first company to nationally offer memory kits to computer hobbyists, we again thank you for choosing ECONOROM 2708... welcome to the club!

# TECHNICAL OVERVIEW

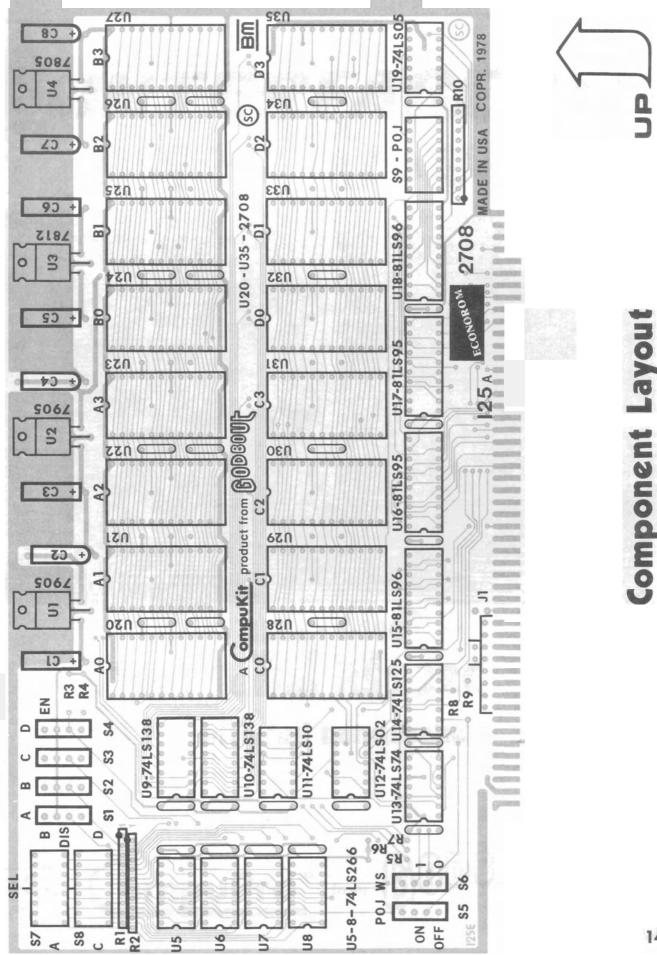

This board provides space for up to 16 2708s, one of the most popular high density EPROMS. EPROMS give the advantage of retaining stored data when power is removed. EPROMS are erasable; that is, after programming they may be erased and reprogrammed with other material. The EPROM locations on this board are grouped in four independent 4K blocks. The on-board DIP switch (no jumpers required) provides addressing on any 4K boundary. Additionally, each 4K block contains an independent disable switch. This board also features a wait state selection switch to select zero or one wait state, provision for use of PHANTOM (line 67), a switch addressed power-on-iump feature, thorough capacitor bypassing of supply lines to suppress noise transients, plus on-board regulation and heat-sinking for reliably cool operation. All this and presoldered sockets for all ICs go onto a double-sided, soldermasked printed circuit board with a complete componentlayout legend. This board provides the user with a highly flexible building block for virtually any S-100 system configuration.

| U | pon re     | ceipt of your kit, check your parts against the list below.                      |  |  |  |  |  |

|---|------------|----------------------------------------------------------------------------------|--|--|--|--|--|

|   | (1)        | ECONOROM 2708 circuit board.                                                     |  |  |  |  |  |

|   | INTE       | GRATED CIRCUITS (note: the following parts                                       |  |  |  |  |  |

|   |            | have letter suffixes and prefixes along with the                                 |  |  |  |  |  |

|   | -          | numbers given below.)                                                            |  |  |  |  |  |

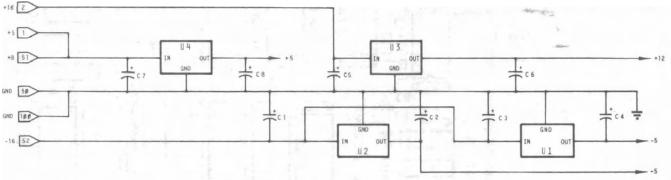

|   | (2)        | 7905 negative 5V regulator (U1 - U2)                                             |  |  |  |  |  |

|   | (1)        | 7812 positive 12V regulator (U3)                                                 |  |  |  |  |  |

|   | (1)        | 7805 positive 5V regulator (U4)                                                  |  |  |  |  |  |

|   | (2)        | 74LS1381 of 8 line decoders (U9 U10)                                             |  |  |  |  |  |

|   | (1)        | 74LS266 exclusive NOR gate (U2)                                                  |  |  |  |  |  |

|   | (1)        | 74LS10 NAND gates (U11)                                                          |  |  |  |  |  |

|   | (1)        | 74LS02 NOR gate (U12)                                                            |  |  |  |  |  |

|   | (1)        | 74LS74 dual flip flop (U13)                                                      |  |  |  |  |  |

|   | (1)        | 74LS125 TRI-STATE* output gates (U14)                                            |  |  |  |  |  |

|   | (2)        | 81LS96/98 TRI-STATE* buffer (U15, U18)<br>81LS95/97 TRI-STATE* buffer (U16, U17) |  |  |  |  |  |

|   | (2)<br>(1) | 74LS05 hex inverter (U19)                                                        |  |  |  |  |  |

|   | (1)        |                                                                                  |  |  |  |  |  |

|   | ОТН        | ER ELECTRONIC COMPONENTS                                                         |  |  |  |  |  |

|   | (3)        | SIP resistor packs (R1, R2, R10)*                                                |  |  |  |  |  |

|   | (27)       | Disc capacitors (C9-C35)*                                                        |  |  |  |  |  |

|   | (7)        | 2.7K 1/4 watt resistors (R3-R9) red, violet, red                                 |  |  |  |  |  |

|   | (4)        | 39uF 10V tantalum capacitors (C5, C6, C7, C8)                                    |  |  |  |  |  |

|   | (4)        | 1.8uF 35V tantalum capacitors (C1, C2, C3, C4)                                   |  |  |  |  |  |

|   | MEC        | HANICAL COMPONENTS                                                               |  |  |  |  |  |

| Π | (3)        | DIP switches (S7, S8, S9)*                                                       |  |  |  |  |  |

| П | (31)       | low profile sockets*                                                             |  |  |  |  |  |

|   | (6)        | slide switches (S1-S6)                                                           |  |  |  |  |  |

|   | (4)        | sets #6 hardware                                                                 |  |  |  |  |  |

| Ē | (4)        | TO-220 heat sinks                                                                |  |  |  |  |  |

#### MEMORY ADDRESS ASSIGNMENT

This board is configured as 4 independent 4K blocks addressable on any 4K boundary. Each 4K block is addressed using the following DIP switch positions:

| Block A | Switch S7 positions 1 - 4 |

|---------|---------------------------|

| Block B | Switch S7 positions 5 - 8 |

| Block C | Switch S8 positions 1 - 4 |

| Block D | Switch S8 positions 5 - 8 |

Each area's address is selected as follows: see errata page 142

| Switch<br>Number                                                                                                                                                                                                                                         | Hex<br>Address                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| 1 2 3 4 or<br>6 7 8 9                                                                                                                                                                                                                                    | and the second |

| $\begin{array}{c} 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 1 & 1 \\ 0 & 0 & 1 & 1 \\ 0 & 1 & 0 & 0 \\ 0 & 1 & 0 & 1 \\ 1 & 0 & 0 & 1 \\ 1 & 0 & 0 & 1 \\ 1 & 0 & 1 & 1 \\ 1 & 1 & 0 & 0 \\ 1 & 0 & 1 & 1 \\ 1 & 1 & 1 & 0 \end{array}$ | 2000                                                                                                             |

| 1111                                                                                                                                                                                                                                                     | F000                                                                                                             |

#### **BOARD ENABLE SWITCHES**

Slide switches S1 through S4 are board enable switches for blocks A through D, respectively. Each switch in the CENTER position *disables* its respective block of memory. Putting each switch in the UP position will *enable* the respective block of memory. When a block is disabled, it is transparent or invisible as far as the machine is concerned (just as if it were non-existent).

This feature allows the board to be used as a 4K, 8K, 12K or 16K board. It also allows the user to have parallel sets of software. For example, suppose you need to run some programs in BASIC, switch over to some other language, then get back to BASIC again. You may have both languages in blocks occupying the same area of memory. When using BASIC, merely disable the block containing the other language. When you wish to switch, disable the BASIC block and enable the other. Note that if 2 blocks share the same address space, only 1 may be enabled at any time.

#### **POWER ON JUMP**

The power on jump feature, when enabled, causes the machine to start at some address other than zero after reset or power on clear. This is accomplished by driving the PHANTOM line low which should disable all system memory, then putting a jump command onto the data in buss, causing the CPU to jump to the desired address. This address can be any multiple of 256 by setting the high order byte of the address on the appropriate DIP switch (switch 9). This feature is *enabled* when slide switch 5 is in the CENTER (ON) position and is *disabled* when this switch is in the DOWN (OFF) position.

#### WAIT STATE SELECT SWITCH

If switch S6 is in the CENTER position, *one* wait state will be added to all memory cycles accessing this board. If the switch is in the DOWN position, no wait states will be added.

#### PHANTOM LINE

In response to increasing numbers of users who have requested inclusion of "PHANTOM" line, (often used for implementing power on jump features) this board is designed for use with active or inactive PHANTOM lines. Boards require a jumper J1 to implement this feature

#### CAUTION

Some manufacturers use the PHANTOM line (buss pin 67) for a refresh signal. This will conflict with the PHANTOM feature and cause boards with PHANTOM to fail. If your system has this conflict, it *must* be resolved by either eliminating the refresh signal on the CPU board or disabling the PHANTOM feature on this and other boards. The PHANTOM feature is disabled if the jumper (J1) is *not connected* on the trace to buss pin 67 (see Figure 11).

If you want the PHANTOM feature, the conflicting refresh signal may be eliminated (IF NOT USED ELSEWHERE IN THE SYSTEM) by cutting the trace connected to buss pin 67 on the CPU board. BE SURE OF YOUR SYSTEM CONFIGURA-TION BEFORE CUTTING ANY TRACES.

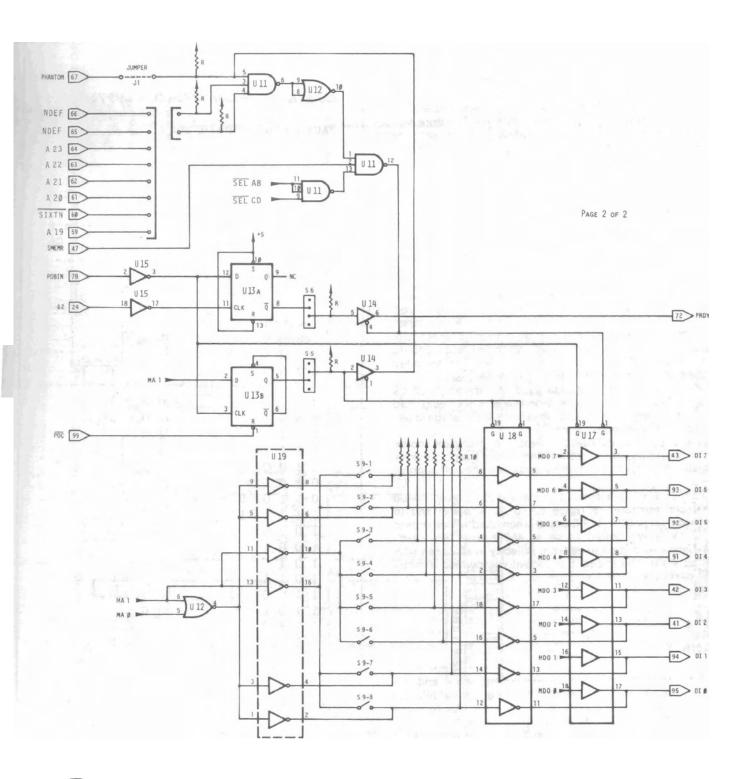

# CIRCUIT DESCRIPTION

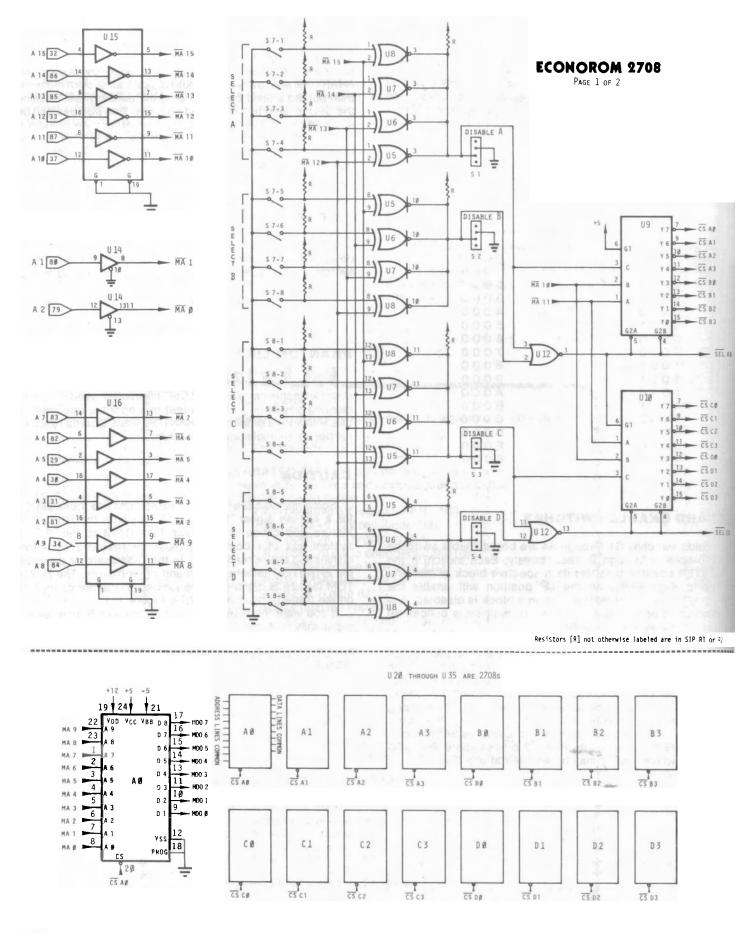

The heart of ECONOROM 2708 is the 2708 erasable, programmable, read-only memory (EPROM), which has 8K bits of storage configured as 1024 bytes of eight bits each. (Thus, each is a "1K x 8" memory IC). These ICs are arranged in blocks of four. This way, each block can store 4K x 8 bits of information. Four of these blocks together produce a total memory storage of 16K x 8 bits.

Now that we have this storage, there are still other aspects we must consider. First, *addressing* a specific address in memory; and second, *reading* from memory.

The logic diagram on pages 8 and 9 show the address circuitry along with the other ECONOROM circuitry. Each memory IC requires 10 address bits (A0-A9) to access any one of the 1024 bytes available in the IC. These address bits are generated by the CPU and are buffered on the ECONOROM. After buffering, a particular address is presented to all memory address selection pins. We must also select which particular IC in any particular block is to react to the given address. This requires 6 more address bits (A10-A15). A12 through A15 are decoded and used to *select* the desired block of ICs. A10 and A11 are decoded and used to *enable* the desired IC in that block.

Data to be read into the data buss from memory passes through 8 TRI-STATE® drivers. When data is not being read onto the buss, the outputs of these drivers are in a high impedance or "disconnected" state.

To prevent IC generated switching transient noise problems, bypass capacitors are tied across the power lines at regular intervals in the memory array and at every support IC.

This board is guaranteed to operate at 2MHz over the full commercial temperature range (0-70° C ambient) and to draw less than 3500 mA (3.5 amps) when used with standard 2708's. We have tested these at 4MHz with "standard" 2708's and found them to operate reliabily in all cases with one wait state. The speed and current will depend directly on the particular 2708's you use.

# THANK YOU

This board is the result of much time, work and experience on the part of a number of people. In addition to thanking you for choosing this board, we'd like to thank everyone involved for their work on this project.

We strive for a board that not only works the first time but continues to give reliable operation for a long time. If we can be of any help to you in applying this board, or if you have any questions, please let us know. As always, we solicit your comments, letters and new product suggestions.

HAPPY COMPUTING!

ERRATA ECONOROM 2708

PARTS LIST should read

- (4) 74LS266 at positions U5, U6, U7 & U8

- (4) 39 uF tantalum capacitors at positions C2, C4, C7 & C8

- (4) 1.8 uF 35V tantalum capacitors at positions C1, C3, C5 & C6

#### MEMORY ADDRESS ASSIGNMENT should read

should lead

|   | Switch<br>Number |   |   |   |    |   |     | Hex<br>Address |     |   |   |

|---|------------------|---|---|---|----|---|-----|----------------|-----|---|---|

| 1 |                  |   | 3 |   | or |   |     |                |     |   |   |

| 6 | ,                | 7 | 8 | 9 |    |   |     |                |     |   |   |

|   |                  |   |   |   |    |   |     |                |     |   |   |

| 0 | )                | 0 | 0 | 0 |    |   |     | 0              | 0   | 0 | 0 |

| 0 | )                | 0 | 0 | 1 |    |   |     | 1              | 0   | 0 | 0 |

| C | )                | 0 | 1 | 0 |    |   |     | 2              | 0   | 0 | 0 |

| C | )                | 0 | 1 | 1 |    |   |     | 3              | 0   | 0 | 0 |

| C | )                | 1 | 0 | 0 |    |   |     | 4              | 0   | 0 | 0 |

| C | )                | 1 | 0 | 1 |    |   |     | 5              | 0   | 0 | 0 |

| 0 | )                | 1 | 1 | 0 | 0  | = | OFF | 6              | 0   | 0 | 0 |

| 0 | )                | 1 | 1 | 1 | 1  | - | ON  | 7              | 0   | 0 | 0 |

| 1 | Ľ                | 0 | 0 | 0 |    |   |     | 8              | 0   | 0 | 0 |

| 1 | L                | 0 | 0 | 1 |    |   |     | 9              | 0   | 0 | 0 |

| 1 | L                | 0 | 1 | 0 |    |   |     | А              | 0   | 0 | 0 |

| 1 | L                | 0 | 1 | 1 |    |   |     | В              | 0   | 0 | 0 |

| 1 | L                | 1 | 0 | 0 |    |   |     | C              | 0   | 0 | 0 |

| 1 | 1                | 1 | 0 | 1 |    |   |     | D              | 0 ( | 0 | 0 |

|   | 1                | 1 | 1 | 0 |    |   |     | E              | : 0 | 0 | 0 |

|   | 1                | 1 | 1 | 1 |    |   |     | F              | 0 י | 0 | 0 |

|   |                  |   |   |   |    |   |     |                |     |   |   |

|   |                  |   |   |   |    |   |     |                |     |   |   |