Step 1: Execute a DI instruction.

Disables interrupts during bank switching.

Step 2: Set current bank variable CURBNK to new bank.

Update the current bank information in CURBNK (ØF534H)

with new bank information.

Step 3: Prepare data for BANKR.

Load system memory area RZBANKR (ØF53DH) for BANKR

(PØ5H).

RZBANKR and BANKR contain the same data.

Step 4: Write data to BANKR.

Output new bank data into BANKR (P05H). The bank data

must be identical to that set up in step 3.

Step 5: Execute an EI instruction.

Enables the CPU for interrupts.

## 4.4.4 Work Areas Associated with Bank Switching

OLDBNK (ØF52CH) 1 byte

Save area loaded with bank information on entry to BIOS.

= ØFFH: System bank

= ØØH: Bank Ø (RAM)

= ØlH: Bank 1

= Ø2H: Bank 2

DISBNK (ØF52EH) l byte

Parameter area for JUMP or CALL bank switching routine.

= ØFFH: System bank

=  $\emptyset\emptysetH$ : Bank  $\emptyset$  (RAM)

= 01H: Bank 1

= Ø2H: Bank 2

BNKRGS (ØF53ØH) l byte

System bank area. Set to 00H.

BNKRGl (ØF531H) 1 byte

Bank Ø area. Set to 40H.

RZBANKR (ØF53DH) 1 byte

System area for holding output data to RANKR (PØ5H).

Has the same format as BANKR.

BNKRG2 (ØF532H) 1 byte

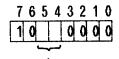

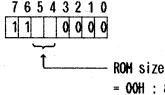

Bank 1 area

- ROM size

= 00H : 8K-byte ROM

= 01H : 16K-byte ROM

= 10H : 32K-byte ROM

8K-byte ROM is assumed when no ROM is installed.

BNKRG3 (ØF533H) 1 byte Bank 2 area

= 00H : 8K-byte ROM = 01H : 16K-byte ROM = 10H : 32K-byte ROM

8K-byte ROM is assumed when no ROM is installed.

CVRBNK (ØF534H) 1 byte

Contains the bank number of the current bank.

= ØFFH: System bank

= 00H: Bank 0 (RAM)

= 01H: Bank 1

= Ø2H: Bank 2

#### 4.5 Resident Processing

#### 4.5.1 General

When resident processing is specified by an application program, the current program in RAM is preserved and when a power-on condition is generated in the restart mode (by the wake function or other factor), control is transferred immediately to address 100H on bank 0.

This function allows the PINE to warm-start an application program at a power-on time without passing through the menu processing or CCP, making it a turn-key system.

When this function is activated, the auto start or wake string is passed to the application program through the keyboard buffer. The application program can treat the string as if it were entered from the keyboard at warm-start time.

4.5.2 How to Specify and Cancel Resident

#### 4.5.2.1 Specifying resident

Resident must be specified within the application program. The method of specifying resident processing differs between ROM-based and load-and-go programs.

Resident can be specified by setting the resident flag RESEXQ (ØEF28H) in the system area in one of the following ways:

1. Calling the BIOS RESIDENT function (WBOOT + 84H).

2. Writing 01H directly into RESEXQ (0EF28H).

- (1) Actions required of a load-and-go program for resident processing A load-and-go program, when started, is loaded into RAM (bank 0) at address 100H, after which control is transferred to address 100H. To specify resident processing, the load-and-go program must take the following steps:

- Set the resident flag.

- If necessary, rewrite the instruction at address 100H to a jump to the point of warm start.

Subsequently, when power-on, reset, or WBOOT processing is initiated, the system transfers control directly to address 100H in RAM.

(2) Actions required of a ROM-based program for resident processing When a ROM-based program is started, the first sector of the program is loaded into RAM (bank 0) at address 100H, after which control is transferred to the specified program start address. The ROM-based program which is to specify resident processing must load necessary data in advance into the first 90 bytes of the ROM program in the specified format (see Section 4.61, "Executing a ROM Program" for the format of the 90-byte data). The ROM-based program need only set the resident flag.

Subsequently, when power-on, reset, or WBOOT processing is initiated, the system transfers control directly to address 100H in RAM. The 90 bytes from address 100H contains the data that was read when the ROM-based program was started for the first time. The data consists of routines for checking for a program for which resident is specified, for transferring control to the given address, and for handling errors.

# 4.5.2.2 Canceling resident processing

Resident processing must be canceled by the application program. Resident can be canceled by:

- 1. Calling the BIOS RESIDENT function (WBOOT + 84H).

- 2. Writing 00H directly into RESEXQ (0EF28H).

The resident flag RESEXQ is not affected by resets; it is cleared to zero only by System Initialize. This means that control cannot exit the application program if the resident flag remains set.

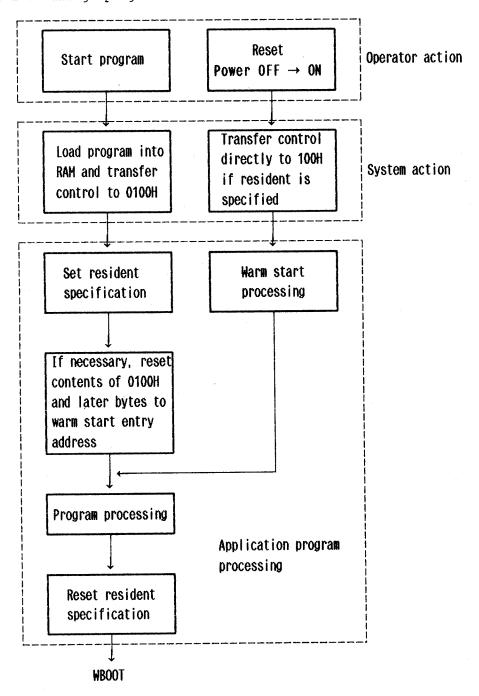

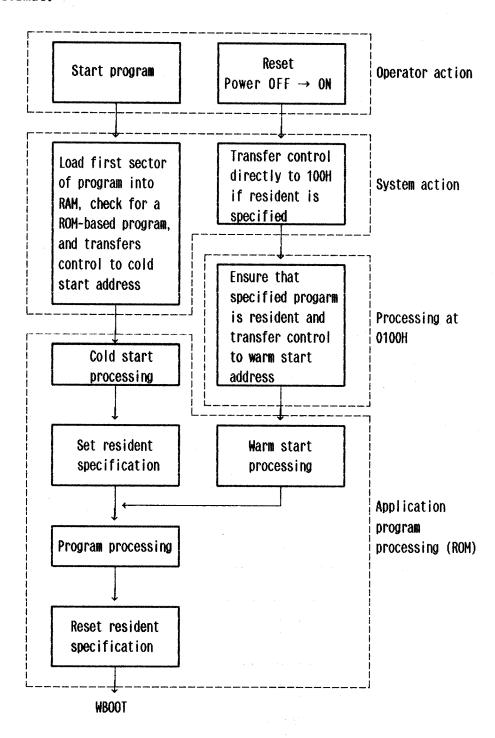

## 4.5.3 Processing Flows

The flowcharts below show the flows of processing of the system and application programs for which resident is specified.

(1) Load-and-go program

(2) ROM-based program ROM-based programs to be executed with resident specified must begin with a 90-byte data area in the specified format. See Section 4.6, "Executing a ROM Program" for the 90-byte data format.

## 4.5.4 Miscellaneous Considerations

#### 4.5.4.1 Programming notes

- (1) Before terminating (calling WBOOT) a program for which resident is specified, cancel the resident specification. Otherwise, the program can be terminated by no means but system initialize.

- (2) When specifying resident processing for a ROM-based program, be sure to define predetermined data in the first 90-byte are of the program in advance. Otherwise, warm start processing will fail.

## 4.5.4.2 Related Work Area

RESEXQ (ØEF28H) l byte Resident flag.

- = 00H: Resident not specified.

- = Nonzero: Resident specified.

The initial value is 00H. This area is initialized only by system initialize.

#### 4.6 Executing a ROM-based Program

#### 4.6.1 General

Although the PINE can load application programs from ROM capsules into RAM memory at address 100H for execution as under standard CP/M, it can also execute the programs as stored in the ROM to increase memory efficiency and to save electric power. This section explains the principle of ROM-based program execution, method of establishing the execution environment, and programming notes.

#### 4.6.2 Establishing the Execution Environment

ROM-based programs, which are executed immediately in a ROM capsule, must be given an identification at their beginning to distinguish themselves from ROM programs, called load-and-go ROM programs, which are loaded into RAM memory for execution.

## 4.6.2.1 When resident is not specified

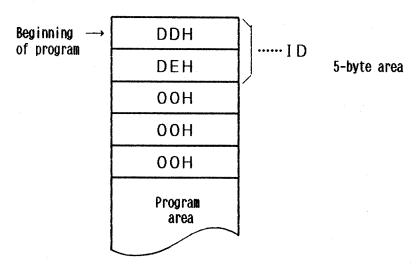

A ROM-based program without resident specification must begin with a 5-byte ID data as shown in the figure below. The system identifies a ROM-based program by examining this field.

# 4.6.2.2 When resident is specified

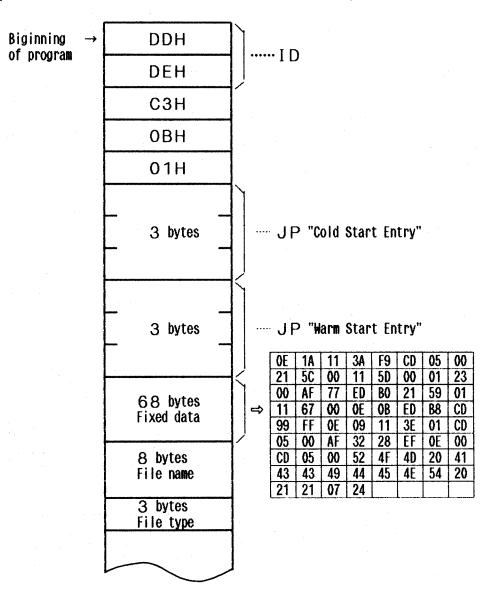

A ROM-based program with resident specified must begin with 90 bytes of information in the format shown below.

| Offset     | Bytes | Name                                              | Description                                                                                                                                                  |

|------------|-------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00H~01H    | 2     | ID                                                | ROM-based program identifier                                                                                                                                 |

| Ø2H~Ø4H    | 3     | Jump<br>instruction<br>for resident<br>processing | I Drocessing (NOD when regident                                                                                                                              |

| Ø5H~Ø7H    | 3     | Cold Start<br>Entry                               | Program cold start address<br>(Jump to ROM cold start<br>address)                                                                                            |

| Ø8H~ØAH    | 3     | Warm Start<br>Entry                               | Program hot start address<br>(Jump to ROM hot start<br>address)                                                                                              |

| ØBH ~ 4 EH | 68    | Resident<br>processing                            | Instructions for resident processing. Resident processing consists of: 1. Setting up DMA and FCB. 2. Executing RSROMEXQ. 3. Abnormal termination processing. |

| 4FH~56H    | 8     | File name                                         | ROM-based program name (must<br>be the same as that in the<br>ROM directory)                                                                                 |

| 57H~59H    | 3     | FILE TYPE                                         | ROM-based program type<br>(must be the same as that in<br>the ROM directory)                                                                                 |

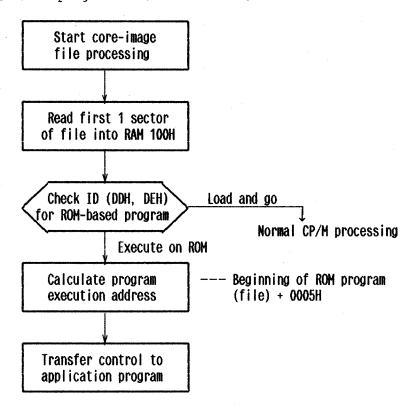

#### 4.6.3 Processing Flow

Figure 4.6.1 shows the flow of processing up to the point where a ROM-based program receives control.

Fig. 4.6.1 Starting a ROM-based Program

## 4.6.4 Use and Programming Notes

This subsection describes the use and programming notes to be taken when programming ROM-based programs.

### 4.6.4.1 Program starting address

Load-and-go ROM programs are loaded into RAM memory at location 100H for execution. Such programs must be allocated RAM memory starting at address 100H. ROM-based programs can execute directly in a ROM capsule. The starting address of such programs must be determined by taking into account the header and directory areas.

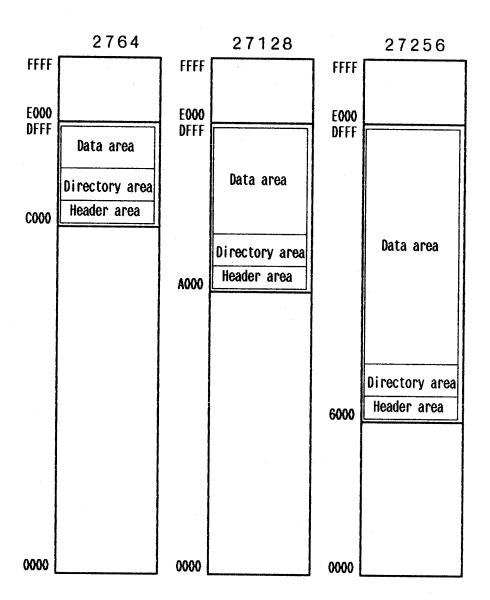

The program starting address differs depending on the size of the ROM-based program and the type of the PROM (27256, 27128, or 2764) in which it is to be stored.

A ROM-capsule must contain header and directory areas. Since the size of the directory area of a program file varies with the number and size of the programs that the file contains (though its header area is fixed at 32 bytes), it is necessary to calculate the size of the directory area to be reserved before actually loading the programs.

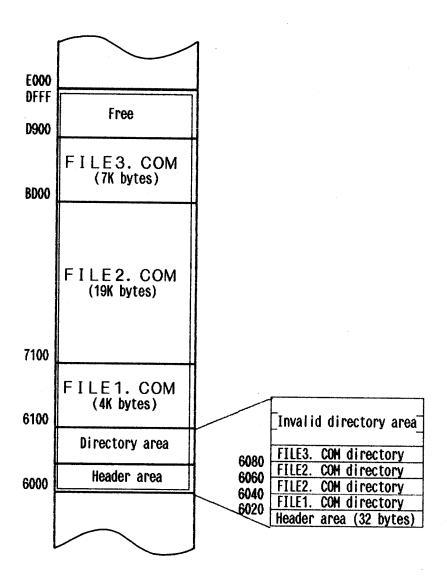

Figure 4.6.2 shows the relationship between the ROMs and PINE addresses.

Note that the physical addresses of 27128 and 27256 ROMs do not match the PINE logical addresses.

When programming a ROM program, use the optional PROM WRITER cartridge or PROMFORM utility program.

Fig. 4.6.2 Relationship between Logical and ROM Addresses (ROM area is enclosed in double boxes)

(1) When implementing a single ROM-based program in a ROM The program starting address of a ROM-based program consisting of a single program is listed below.

| ROM              | 2764   | 27128  | 27256 |

|------------------|--------|--------|-------|

| Starting address | ØСØ8ØН | ØAØ8ØH | 6080H |

A ROM-based program of this type must begin with a 32-byte header and a 32 bytes x 3 directory area. Accordingly, the program starting address must be 80H bytes away from the beginning of the See Section 7.3, "Guide for Programming ROMs" for the structure of the header and directory areas.

(2) When implementing more than one ROM-based program in a ROM When implementing more than one ROM-based program in a ROM, it is necessary to calculate in advance the size of the directory area to be reserved since the size of a portion of the directory area varies with the number of programs and ROM capacity.

One directory entry can handle a file of up to 16K bytes. Two or more entries are used to handle files larger than 16K bytes. For example, two directory entries are required for a ROM-based program larger than 16K bytes and one directory entry for one which is smaller than 16K bytes.

Since the directory area (including the header area) is reserved in 128-byte increments, the size of space necessary for the header and directory areas is obtained from the formula:

$[\{((n1/16384 + 1) + (n2/16384 + 1) + ...) / 4\} \times 4 + 1] \times 32$  by test

Number of directory entries

Total number of directory entries

For 128-byte boundary alignment

(16K = 16,384)

where nl, n2, ... denote program sizes.

The program starting address is obtained by adding the above result to the starting address of the ROM.

To find the starting address of the second and subsequent programs, follow the steps given below.

Since CP/M manages files in lK-byte units, the starting address of the second or subsequent program is obtained by adding the starting address of the preceding program plus  $[{(n-1)/1024} + 1] \times 1024$ (bytes)

where n is the size of the preceding program.

Figure 4.6.3 shows the memory map for the following ROM programs implemented in a 27256 ROM:

|           |         |             | T                 |                  |

|-----------|---------|-------------|-------------------|------------------|

| File name | Records | File size   | Directory entries | Starting address |

| FILE1.COM | 1 30    | 4K bytes    | 1                 | 6100H            |

| FILE2.COM |         | 19K bytes   | 2                 | 7100H            |

|           |         | 7K bytes    | 1                 | BDØØH            |

| FILE3.CON | שכ ן וי | 1 / V DAres | 1                 |                  |

Fig. 4.6.3 Sample ROM Memory Map (for PINE)

byte

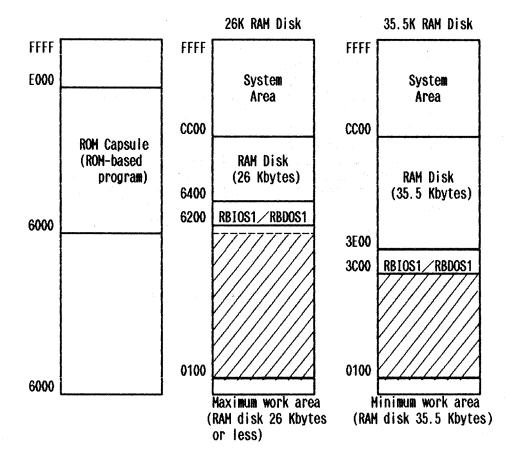

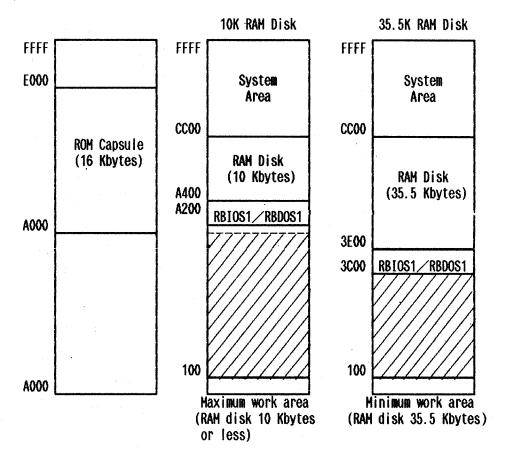

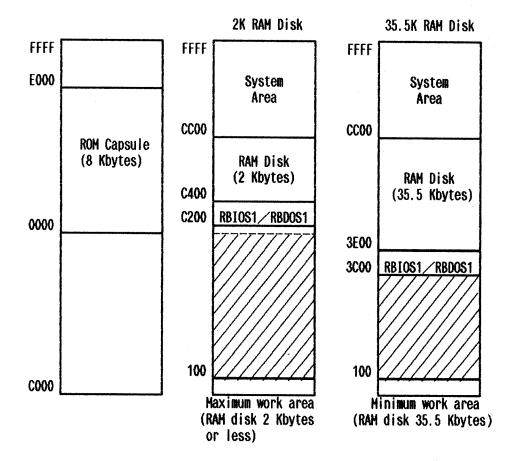

(2) ROM-based Program Work Areas ROM-based programs need a work area which is different from that used by load-and-go programs. Whereas load-and-go programs can use the area following their program area as a work area, ROM-based programs must use an area higher than 100H (15AH or higher when Resident is specified). The upper limit of the work area for ROM-based programs is obtained as follows:

min{(ROM Starting Address), (RBDOS1 Starting Address)}

The ROM starting address is: 6000H for 27256 0A000H for 27128 0C000H for 2764

The RBDOS1 staring address is stored in addresses 0006H and 0007H.

a) When 27256 ROM is used

The hatched area is available as the work area without bank switching. The area starting at 6000 H is made available through bank switching.

#### b) When 27128 ROM is used

The hatched area is available as the work area without bank switching. The area starting at address ØAØØØH is made available through bank switching.

## c) When 2764 ROM is used

The hatched area is available as the work area without bank switching. The area starting at address ØC000H is made available through bank switching.

(3) BDOS/BIOS Calls from ROM-based Programs

Load-and-go programs call address 0005H through 0007H when making a BDOS call and address 0000H through 0002H when making a BIOS call. For ROM-based programs, however, the addresses of BDOS and BIOS may be located in the background memory of the ROM capsule (because their location varies with the capacity of the installed RAM disk). When calling BDOS and BIOS, therefore, ROM-based programs must call BDOS and BIOS entry points (RBDOS2 and RBIOS2) in the resident area.

RBDOS2 entry address: ØFF9ØH (JP RBDOS2)

RBIOS2 BOOT address: ØEBØØH RBIOS2 WBOOT address: ØEBØ3H RBIOS2 CONST address: ØEBØ6H

RBIOS2 CONTINUE address: ØEB8AH

(4) ROM-based program ROMs

The PINE supports two formats, P- and M-formats, for ROM

capsules. ROM-based programs must be programmed in the P-format.

Load-and-go ROM programs may be programmed either in the P- or Mformat. See Section 7.3, "Guide for Programming ROMs" for

instructions for programming ROMs.

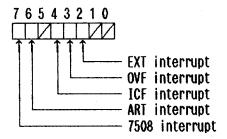

## 4.7 Interrupts

#### 4.7.1 General

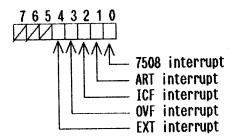

PINE supports five types of interrupts. When an interrupt occurs, it takes in and sets up the corresponding interrupt vector and transfers control to the interrupt processing routine.

The interrupts that the PINE supports include:

- 1. 7508 (4-bit CPU)

- ART (RXRDY)

- 3. Alarm time

- 4. ICF (Input Capture)

- OVF (FRC Overflow)

- EXT (External)

The sources of 7508 interrupts are:

- 1. Keyboard

- 2. Power switch

- Alarm time

- 4. Power fail

- 1-second interrupt

#### 4.7.2 Interrupt Vector

The PINE handles five types of interrupts. Their interrupt vector table is located in the area between ØFFFØH and ØFFFFH.

Interrupts are given priorities; the PINE accepts interrupts of the highest priority first.

Table 7.4.1 Interrupt Vector Table

| Priority    | Interrupt source         |      | RAM address       |

|-------------|--------------------------|------|-------------------|

| 1 (highest) | 7508 (4-bit CPU)         | ØFØH | ØFFFØH and ØFFF1H |

| 2           | ART (RXRDY)              | ØF2H | ØFFF2H and ØFFF3H |

| 3           | ICF (Input Capture)      | ØF4H | ØFFF4H and ØFFF5H |

| 4           | OVF (FRC Overflow)       | ØF6H | ØFFF6H and ØFFF7H |

| 5           | EXT (External interrupt) | ØF8H | ØFFF8H and ØFFF9H |

The interrupt sources and their reset conditions are listed in Table 4.7.2.

Table 4.7.2 Interrupt Sources and Reset Conditions

| Interrupt      | Interrupt source                                                                                               | Reset conditions                                          |

|----------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| 75Ø8           | * Keyboard input  * Lapse of 1 second  * Alarm time  * Power switch on or off  * Power fail voltage            | Returns a reply to the 7508.                              |

| ART<br>(RxRDY) | * ART RxRDY set.                                                                                               | Reads the receive data register ARTDIR (P14H).            |

| ICF            | * Change in state of<br>the input signal from<br>barcode reader or<br>cassette drive                           | Reads the input capture register (P03H).                  |

| OVF            | * FRC (Free Running<br>Counter) overflows.<br>FRC is a 16-bit coun-<br>ter running at a<br>period of 106.7 ms. | Issues a Reset OVF command (sets CMDR (P02H) bit 2 to 1). |

| EXT            | * Interrupt signal from external device (via system bus)                                                       | Returns a reply to the external device (via system bus).  |

## 4.7.3 Interrupt Control

The PINE takes various actions to control interrupts.

## 4.7.3.1 Setting up the interrupt mode and vector data

When an address 0000H start occurs (started by a system initialize, reset, or power-on), the PINE specifies the mode 2 interrupt and loads the I register with 0FFH (the higher order 2 digits of the interrupt vector table address).

## 4.7.3.2 Loading the interrupt vector table

The PINE loads interrupt data from OS ROM into addresses  $\emptyset$ FFF $\emptyset$ H through  $\emptyset$ FFFFH when a reset or system initialize occurs.

- 4.7.3.3 Interrupt control (disabling and enabling)

- (1) Interrupt control by the system

The PINE system disables and enables interrupts as follows:

Table 4.7.3 Interrupt Control

| Interrupt                 | 7<br>5 |     | 750  | 8     | A  | 0      | I      | Ë | 2                                                                               |

|---------------------------|--------|-----|------|-------|----|--------|--------|---|---------------------------------------------------------------------------------|

| Processing                | 0<br>8 | key | 1sec | Alarm | R  | V<br>F | C<br>F | X | Remarks                                                                         |

| System Initialize         |        | 0   | 0    | ×     | ×  | 0      | X      | × | This                                                                            |

| Reset                     | 0      | 0   | 0    |       | X  | 0      | X      | × | state                                                                           |

| Restart Pw ON             | 0      | _   |      | _     | X  | 0      | ×      | × | continues.                                                                      |

| Continue Pw ON            |        | _   | _    | _     | _  | _      | _      | _ |                                                                                 |

| 7508 interrupt processing | ×      | _   | _    | _     | _  | _      | _      | _ | Enabling<br>the CPU<br>for<br>interrupt<br>of 7508<br>during<br>alarm<br>screen |

| ART interrupt processing  | ×      | _   | -    | _     | ×  | ×      | ×      | × | display                                                                         |

| OVF interrupt processing  | ×      |     |      |       | ×  | ×      | ×      | × | Continues<br>process-                                                           |

| ICF interrupt processing  | ×      | _   | -    |       | ×  | ×      | ×      | × | ing in<br>DI state                                                              |

| EXT interrupt processing  | ×      |     | _    | _     | ×  | ×      | ×      | × |                                                                                 |

| MCT processing            | ×      | _   | _    | _     | _  | ×      |        | - |                                                                                 |

| FDD processing            | ×      |     | _    | -     | ×  | ×      | ×      | × | Continues<br>process-<br>ing in DI<br>state.                                    |

| BEEP processing           | -      | △*  |      | _     | -* | ×      | -*     | * | *                                                                               |

indicates that the interrupt disable/enable state can be changed during processing.

O··· Enabled ×··· Disabled -··· No change

$<sup>\</sup>Delta \cdots$  Disables all interrupts except STOP key interrupts.

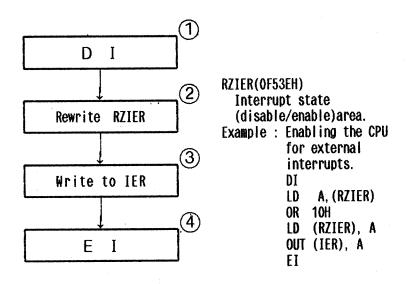

(2) Disabling or enabling interrupts

The PINE CPU can be disabled or enabled for interrupts by:

1. Using the BIOS MASKI function.

Rewriting the Interrupt Enable Register (IER) (PØ4H) directly.

See Section 3.4, "BIOS Details" for the use of the BIOS MASKI function.

The figure below shows the steps for rewriting the IER directly.

Fig. 4.7.4 Rewriting IER

Related work area: RZIER (ØF53EH) 1 byte Contains the interrupt disable/enable status.

l refers to enabling and a  $\emptyset$  to disabling interrupts. The format of the RZIER is identical to that of the IER.

# 4.7.3.4 Interrupt processing time

Table 4.7.5 lists the times required for the PINE to process interrupts.

Table 4.7.5 Interrupt Processing Times

| Interrupt         | Number of<br>machine states | Time              | Remarks                                                   |

|-------------------|-----------------------------|-------------------|-----------------------------------------------------------|

| 7508 (key in)     | 13789                       | 3747µs            |                                                           |

| 7508 (1 sec)      | 14141                       | 3842µs            |                                                           |

| 7508 (Alarm)      | 14087                       | 3828µs            | Processing time when alarm display processing is disabled |

| 7508 (Pw sw on)   | 13837                       | 3760µs            |                                                           |

| 7508 (Pw sw off)  | 175852                      | 47786µs           | Processing time when power-off processing is disabled     |

| 7508 (Power fail) | 13891                       | 3775µs            | Processing time when power-off processing is disabled     |

| ART               | 1623                        | 441µs             |                                                           |

| OVF               | 1122<br>(4504)              | 305µs<br>(1224µs) |                                                           |

| ICF               | 686                         | 186µs             |                                                           |

| EXT               | 698                         | 190µs             |                                                           |

Note: The reason that the interrupt processing times during power-off processing are longer than usual is that the PINE waits for approximately 40 ms after issuing a keyboard clear command to the 7508.

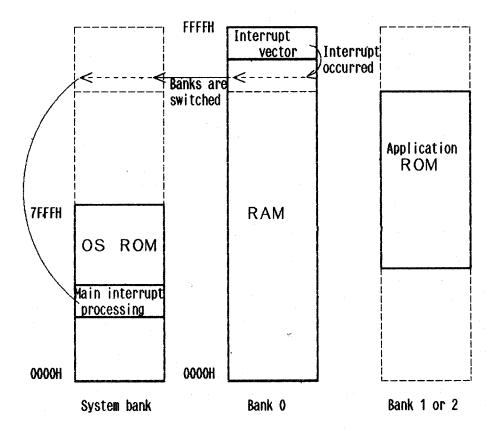

#### 4.7.3.5 Interrupt processing

(1) Location where interrupt processing is performed It is unpredictable on which bank the PINE is running when an interrupt occurs. To keep track of the location of PINE execution when an interrupt occurred, the PINE places the entry portion of the interrupt processing in the resident area (ØEØØØH through ØFFFFH). When an interrupt occurs, the banks are switched in the entry portion and the actual interrupt processing is carried out in the main interrupt processing routine on the OS ROM.

Fig. 4.7.6 Interrupt Processing When an Interrupt Occurred

(2) Relationship between Interrupt processing and BIOS There are some types of interrupts which, when generated during BIOS processing, prevent the PINE from continuing program execution on return from interrupt processing or from performing successful power-off processing in the continue mode if it processes the interrupt immediately.

To solve this problem, the PINE sets the BIOS in-process flag on entry to BIOS (PREBIOS) and, if an interrupt occurs when this flag is on, causes the interrupt processing routine only to set the interrupt flag to memorize the occurrence of an interrupt. At the end of BIOS processing after the return from the interrupt processing, the PINE tests the interrupt flag and, if it is found to be set, performs the actual interrupt processing at the exit of BIOS (PSTBIOS).

BIOS functions which contain loops (e.g., CONIN, RSIN, and RSOUT) also test the interrupt flag as PSTBIOS does and invoke necessary interrupt processing accordingly.

See also Section 3.3, "BIOS Operations" for details on PREBIOS and PSTBIOS.

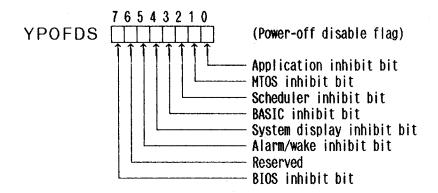

- (3) Inhibiting interrupts

The PINE can inhibit the system from performing interrupt

processing under program control. Interrupt processing that can

be inhibited in this way includes:

- Power-off processing and power fail processing

- 2. Alarm/wake processing

"Disabling interrupts under program control" means that the PINE accepts interrupt requests but inhibits the execution of the corresponding interrupt processing.

This facility is used by PREBIOS and PSTBIOS. Application programs can use this facility to temporarily inhibit power-off or alarm processing while they are taking specific actions.

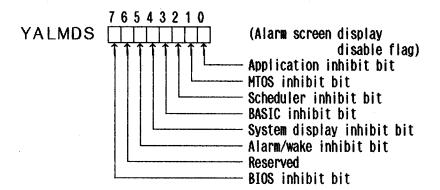

a) How to inhibit interrupt processing PINE OS uses the YPOFDS (ØEFEFH) and YALMDS (ØEFF1H) flag areas for inhibiting power-off and alarm/wake processing. The format of these areas are shown below.

Setting the corresponding bit to 1 inhibits power-off or alarm screen display processing.

During interrupt processing, the system copies the values of YPOFDS and YALMDS into YPOFST (ØEFFØH) and YALMST (ØEFF2H). If YPOFST or YALMST contains ØØH, the system performs power-off or alarm screen display processing; if both YPOFST and YALMST contains nonzero values, the system does nothing and terminates the interrupt processing.

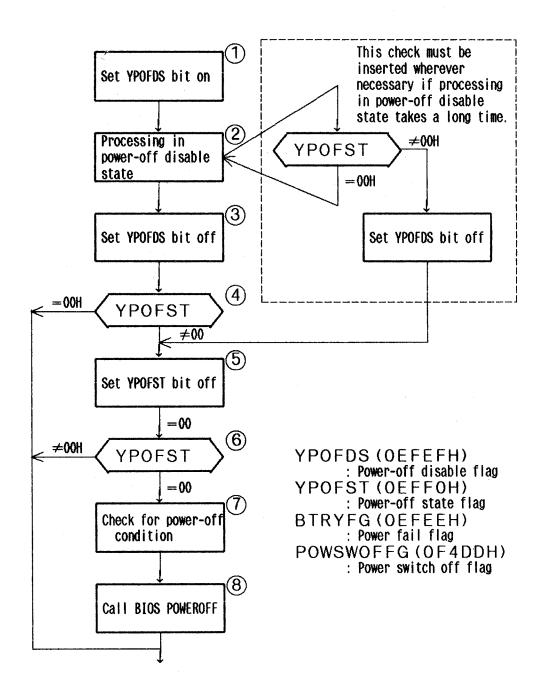

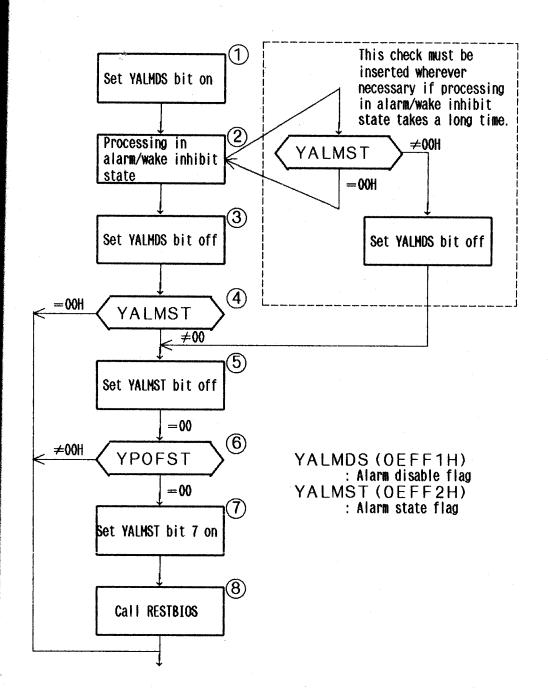

b) Procedures for inhibiting interrupt processing Figures 4.7.7 and 4.7.8 show the procedures for inhibiting interrupt processing. Application programs can manipulate only bit  $\emptyset$  of YPOFDS and YALMDS and must not use the other bits.

Fig. 4.7.7 Procedure for Inhibiting Power-off Processing

- Step 1: Set YPOFDS bit on. Set the specified YPOFDS (ØEFEFH) bit to 1. The application program must use bit Ø.

- Step 2: Processing in power-off disable state. Perform the processing to be executed in the power-off disabled state. A power-off check routine must be inserted wherever

necessary if the processing in power-off disable state takes a long time.

Step 3: Set YPOFDS bit off.

Set the YPOFDS bit that is set to 1 in step 1 to  $\emptyset$ .

Step 4: Check YPOFST. Tests the value of YPOFST (ØEFFØH).

A nonzero value in YPOFST indicates that a power-off interrupt occurred while power-off processing was inhibited.

Step 5: Set YPOFST bit off. Set the YPOFST bit that is set to 1 in step 1 to  $\emptyset$ .

Step 6: Check YPOFST. Test the value of YPOFST (ØEFFØH). A nonzero value in YPOFST indicates that power-off processing is inhibited by another module.

Step 7: Check for power-off condition. Check the power-off conditions. A nonzero in BTRYFG (ØEFEEH) indicates a continue mode power-off condition. If BTRYFG contains 00H, the system examines PWSWOFFG (0F4DDH). A 02H in PWSWOFFG indicates the restart condition and the other values indicate the continue-mode power-off condition.

Step 8: Call BIOS POWEROFF. Call BIOS POWEROFF specifying the power-off condition found in step 7 specified.

Fi

Fig. 4.7.8 Procedure for Inhibiting Alarm Screen Display Processing

- Step 1: Set YALMDS bit on.

Set the specified YALMDS (ØEFF1H) bit to 1. The application program must use bit 0.

- Step 2: Processing in alarm/wake inhibit state.

Perform the processing to be executed in the alarm/wake screen display inhibit state.

A alarm/wake check routine must be inserted wherever necessary if the processing in alarm/wake inhibit state takes a long time.

- Step 3: Set YALMDS bit off. Set the YALMDS bit that is set to 1 in step 1 to  $\emptyset$ .

- Step 4: Check YALMST.

Tests the value of YALMST (ØEFF2H).

A nonzero value in YALMST indicates that an alarm interrupt occurred while alarm/wake processing was inhibited.

- Step 5: Set YALMST bit off.

Set the YALMST bit that is set to 1 in step 1 to 0.

- Step 6: Check YALMST.

Test the value of YALMST (ØEFF2H).

A nonzero value in YALMST indicates that alarm/wake screen display processing is inhibited by another module.

- Step 7: Set YALMST bit 7 on.

Set bit 7 of YALMST (ØEFF2H) to 1. This enables alarm/wake screen to be displayed by PSTBIOS.

- Step 8: Call RSPSTBIOS.

Call RSPSTBIOS (ØFF96H) to display the alarm/wake screen.

- c) Programming notes

- While the system is waiting for keyboard data with BIOS CONIN, it unconditionally executes power switch off, power fail, and alarm/wake processing even if they are inhibited. This also applies to BIOS which is waiting for send or receive data or for a printer ready signal (except during hardcopy processing).

- 2. Checks must be made for power-off or alarm/wake conditions if processing in the power-off or alarm/wake processing disabled state is to take a long time.

```

POWER OFF & ALARM CONTROL PROGRAM

NOTE:

This sample program shows how to control power off & alarm interrupt.

<> assemble condition <>

.Z80

loading address <>

.PHASE 100H

constant values <>

BIOS entry

EB03

WBOOT

CONST

CONIN

EQU

EQU

EQU

Warm Boot entry

Console status entry

Console in entry

Console out entry

Power off entry

0EB03H

EB06

WBOOT

WBOOT

WBOOT

+03H

EB09

EBOC

CONOUT

+09H

POWEROFF

EQU

WBOOT

System area

YPOFDS

YPOFST

YALMDS

YALMST

EFEF

OEFEFH

OEFFOH

Power off disable flag.

Power off status.

Alarm disable flag.

EFF0

EFF1

EFF2

EQU

EQU

OEFF1H

OEFF2H

Alarm status.

Power fail status.

BTRYFG

EQU

OFFEEH

EFFO

EQU

OEFFOR

Power sw, off status.

RAM jump table

FF96

RSPSTBIOS

EOU

OFF96H

; Post BIOS execute.

0003

STOP

EQU

03H

STOP code

Line feed

LF

CR

000A

EQU

; Carriage return

EQU

MAIN PROGRAM

NOTE :

This program is setting power off & alarm alarm disable, and if key inputed, do power

off or alarm,

0100

MAIN:

0100

31 1000

LĐ

SP,1000H

; Set stack pointer.

0103

CD 0121

CALL

DISABLE

; Interrupt disable.

0106

MAINIO:

LD

OR

JP

0106

0109

3A 0237

A, (PEND)

Stop key check.

Stop key pressed?

Yes.

C2 011B

010A

NZ, MAIN20

010D

HALT

CALL

JR

; Wait until interrupt happened,

; Check interrupt status.

; Neither power off nor alarm

010E

0111

CD 0144

28 F3

CHKINT

Z,MAIN10

PUSH

CALL

POP

0113

F5

CD 0185

AF

KEYIN

AF

; Save interrupt information,

; Message display and key in.

; Restore interrupt information.

0114

0117

;

0118

CD 019F

CALL

OKINT

; Interrupt execute.

011B

MAIN20:

011B

CD 0132

C3 EB03

CALL

JP

; Interrupt enable, ; End,

WROOT

*************

DISABLE POWER OFF & ALARM

Disable the following system function.

Power off execute.

Alarm screen display.

<> entry parameter <>

NON

<> return parameter <>

NON

<> preserved registers <>

NON

CAUTION :

0121

DISABLE;

0121

3A EFEF

F6 01

A, (YPOFDS)

Set power off disable.

Bit 0 is application bit.

OR

LD

32 EFEF

0126

(YPOFDS),A

;

3A EFF1

F6 01

32 EFF1

C9

0129

LD

OR

LD

A,(YALMDS)

Set alarm disable.

Bit 0 is application bit.

012C

012E

0131

(YALMDS),A

;

```

```

ENABLE POWER OFF & ALARM INTERRUPT

NOTE :

<> entry parameter <>

NON

<> return parameter <>

NON

preserved registers <>

NON

CAUTION :

0132

0132

0135

ENABLE:

21 EFEF

CB 86

HL, YPOFDS

LD

; Reset my disable bit.

RES

0,(HL)

0137

21 EFF1

T.D

BL.YALMDS

Reset my disable bit.

013A

CB 86

RES

0,(HL)

CD 0144

C8

CD 019F

013C

CHKINT

CALL

Check interrupt happened.

013F

No interrupt.

Interrupt execute.

0140

CALL

OKINT

0143

C9

RET

CHECK POWER OFF & ALARM INTERRUPT

NOTE :

Check power off & alarm interrupt occurred. If occurred, set the information to return

<> entry parameter <>

NON

NON

> return parameter

Z-flag : Return information.

=0 -- Both interrupt not occurred.

=1 -- Interrupt cocurred

A : Interrupt type

bit 0 : Alarm interrupt.

bit 1 : Power off interrupt.

( l=occurr, 0=not occurr)

preserved registers <>

NON

CAUTION

If STOP key is pressed, then sets

PEND flag.

0144

0144

0147

CHKINT:

CD EB06

CALL

CONST

; Key in check.

; No inputed key?

; Yes.

INC

JR

20 OA

NZ, CHK10

014A

014D

014F

CALL

CP

JR

; Get key code.

; STOP key?

; No.

CD EB09

CONIN

FE 03

20 03

NZ,CHK10

;

0151

32 0237

LD

(PEND),A

; Set program end flag.

0154

0154

CHE 10:

0E 00

LD

C', 00H

; Clear return information.

0156

3A EFF0

Check power off status

Power off occurred?

LD

A. (YPOFST)

0159

015A

B7

28 10

OR

JR

2, CHK 20

No.

015C

21 EFEF

CB 86

LĐ

HL, YPOFDS

; Reset my disable bit.

015F

RES

0,(HL)

0161

E6 FE

AND

11111110B

Reset my status bit.

0163

0166

32 EFF0

20 04

LD

JR

(YPOFST), A

NZ, CHK20

Disable by other.

0168

0169

016B

79

F6 02

4F

LD

OR

A,C

02H

Set Power-off- go bit.

LD

016C

CHK20:

016C

016F

0170

3A EFF2

B7

LD

A, (YALMST)

Check alarm status.

OR

JR

Alarm occurred?

A

Z, CHK40

28 10

0172

21 EFF1

I.D

HL . YALMDS

Reset my disable bit.

0175

CB 86

RES

AND

LD

JR

11111110B

(YALMST).A

NZ,CHK40

0177

E6 FE

Reset my status bit.

0179

017C

32 EFF2

20 04

Disable by other.

79

F6 01

4F

017E

LD

A,C

01H

Set alarm-go bit.

017F

OR

LD

0181

C,A

0182

CHEAO:

0182

0183

79

B7

LD

OR

RET

A,C

Set return information.

C9

```

```

STATUS DISPLAY & KEY IN

NOTE ;

If power off or alarm occurred, then display message & wait until key inputed.

<> entry parameter <>

A : Interrupt type,

bit 0 : alarm

bit 1 : power off

<> return parameter <>

NON

NON

CAUTION :

0185

KEYIN;

; Alarm bit --> CY;

; Save interrupt status.

; Alarm happen message.

; Display if alarm occurred.

; Restore interrupt status.

; Power off bit --> CY;

; Power off happen message.

; Display if power off occurred.

0185

0186

RRCA

F5

21 01D3

DC 01C7

PUSH

LD

CALL

POP

0187

018A

018D

HL, MSG01

C, DSPMSG

AF

RRCA

21 01EF

LD

CALL

018F

HL,MSG02

0192

DC 01C7

C, DSPMSG

0195

21 021A

CD 01C7

HL,MSG03

: Key in message

0198

CALL

DSPMSG

j

CD EB09

019R

CONIN

CALL

RET

; Input any key.

019E

POWER OFF OR ALARM EXECUTE

Power off or alarm execute in this routine.

entry parameter <>

A : Interrupt type.

bit 0 : alarm

bit 1 : power off

<> return parameter <>

NON

y preserved registers <>

NON

NON

CAUTION :

019F

019F

OKINT:

F5

CB 4F

28 13

PUSH

AF

Save interrupt information. Power off?

0140

1, A

Z, OK20

01A2

JR

;

01A4

01A6

OE OO

3A EFEE

B7

LD

LD

OR

JR

Set continue power off mode.

Power fail check.

Power fail?

С,00Н

A, (BTRYFG)

01A9

01AA

20 08

NZ,OK10

į

3A EFF0

FE 02

28 01

; Power off check,

; Continue power off?

; Yes.

01AC

LD

CP

A,(PWSWOFFG)

01AF

01B1

JR

Z, OK10

í

01B3

00

c

INC

; Set restart power off.

ðk10:

CD EB7E

01B4

CALL

POWEROFF

; Go power off,

ok20;

01B7

01B7

01B8

AF

0,A

Z

; Restore interrupt information.

F1

CB 47

POP

BIT

Alarm?

01BA

RET

; No.

'n

01BB

3A EFF2

; Set BIOS bit

A,(YALMST)

10000000B

LD

01BE

01C0

F6 80

32 EFF2

OR

LD

(YALMST), A

RSPSTBIOS

01C3

CD FF96

CALL

; Go alarm.

01C6

C9

RET

DISPLAY MESSAGE UNTIL FIND OOH

NOTE :

preserved registers <>

NON

CAUTION :

01C7

01C7

01C8

01C9

DSPMSG

4E

0C

0D

LD

INC

C,(HL)

; Get message data,

End

Yes.

DEC

RET

End of message?

01CA

01CB

E5

PUSH

HL

; Save pointer.

```

```

01CC

01CF

01D0

01D1

CD EBOC

E1

23

18 F4

CALL

POP

INC

JR

CONOUT

HL

HL

DSPMSG

Message display.

Restore pointer,

Poiner update,

Loop

Message

and work area

MSG01;

01D3

01D7

01DB

01DF

01E3

01E7

01EB

01EC

41 6C 61 72

6D 20 69 6E

74 65 72 72

75 70 74 20

6F 63 63 75

72 72 65 64

2E

OD OA OO

DB

'Alarm interrupt occurred.'

DB

CR,LF,OOH

;

MSG02:

01EF

01EF

01F3

01F7

01FB

01FF

0203

0207

020B

020F

0213

0217

50 6F 77 65

72 20 73 77

69 74 63 68

20 6F 72 20

50 6F 72 20

50 6F 77 62

72 20 66 61

69 6C 20 6F

63 63 75 72

72 65 64 2E

0D 0A 00

'Power switch off or Power fail occurred.'

DB

CR, LF, OOH

021A

021A

021E

0222

0226

022A

022E

0232

0234

MSG03;

50 72 65 73

73 20 61 6E

79 20 6B 65

79 20 74 6F

20 63 6F 6E

74 69 6E 75

65 2E

0D 0A 00

DB

Press any key to continue.

DΒ

CR, LF, OOH

PEND;

0237

0237

00

DB

оон

; Program end flag.

```

END

() T

S

h

(; U t e j l

2

3

4

5

(Wpit12

S

## 4.7.3.6 Extending interrupt processing

Interrupt processing can be extended by:

- Using interrupt hooks.

- 2. Rewriting the interrupt vector.

- 3. Checking the interrupt state.

- (1) Extending interrupt processing using interrupt hooks. The interrupt hooks that the PINE supports include ICFHOOK, OVFHOOK, EXTHOOK, and HK8251 (OS kana V2.0 (in Japan) only). See Section 4.3, "Hooks" for the location and the user of these hooks.

- (2) Extending interrupt processing by rewriting the interrupt vector User-supplied interrupt processing can be executed by rewriting the interrupt jump vector (ØFFFØH through ØFFFFH). The user must exercise care with the following when rewriting the interrupt jump vector:

- Rewrite the jump vector after disabling the CPU for interrupts (DI state).

- Place the new interrupt processing routine in the resident area between ØEØØØH through ØFFFFH, that is, the new vector entry must point to somewhere between ØEØØØH and ØFFFFH.

- The interrupt processing routine must reserve its own stack area.

- The interrupt processing routine must not use BDOS or BIOS.

- 5. On exit, restore the registers into the original state established when it is entered (in other words, all registers must be preserved).

- (3) Checking the interrupt state With this method, the interrupt processing routine does not perform interrupt processing immediately but checks for interrupts frequently. The occurrence of interrupts can be tested by examining the following:

- Interrupt flag INTTYPE (ØEFD3H)

- Interrupt Status Register (ISR) (PØ4H)

See Part I, "Firmware" for ISR.

INTTYPE (ØEFD3H) l byte Interrupt flags

When an interrupt occurs, the corresponding bit position is set to 1.

## 4.7.4 7508 Interrupts

#### 4.7.4.1 Outline

When an interrupt is generated by the 7508, the interrupt processing routine reads the 7508 status through the serial communication interface, and transfers control to the corresponding routine that services the interrupt. The routines that service 7508 interrupts include:

Key interrupt 1-second interrupt Power fail interrupt Alarm interrupt Power switch interrupt

7508 interrupt processing allows multiple 7508 interrupts so that the PINE can accept key inputs while displaying the alarm screen.

## 4.7.4.2 Multiple interrupt processing

Provisions are made in 7508 interrupt processing so that multiple 7508 interrupts can be honored.

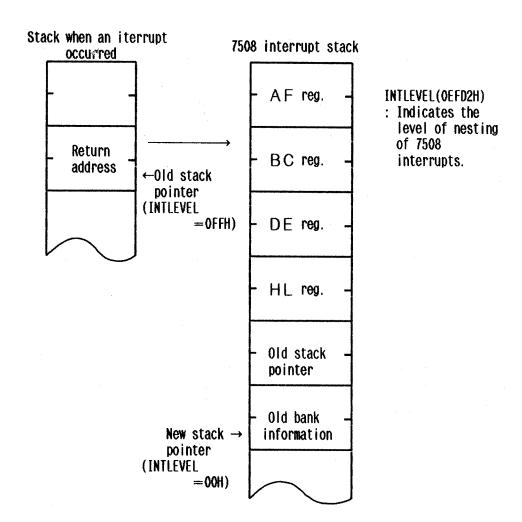

Multiple interrupt processing is accomplished using the interrupt level work area INTLEVEL (ØEFD2H) and stacks. The stacks used for multiple interrupt processing are illustrated below.

The stack status in the above figure shows the one when a 7508 interrupt occurred. If another 7508 interrupt occurs in this condition, the interrupt processing routine does not switch the stacks, but saves the contents of 7508 interrupt stack, from AF register to old bank information, and increments INTLEVEL by 1.

Fig. 4.7.9 Multiple 7508 Interrupt Processing

## 4.7.4.3 Types of 7508 interrupts

There are five types of 7508 interrupts which can be identified by reading the 7508 status.

When an interrupt is generated by the 7508, the system issues a Status Read command (02H) to the 7508 to read the 7508 status. A status value 0BFH or smaller indicates a hard code generated by a key interrupt and a status value 0C0H or greater indicates a power switch, 1-second, alarm, or power fail interrupt. The system stores this status in STS7508 (0F4D6H).

Power switch interrupts are further divided into power switch on and off interrupts. After loading the status of the interrupt (power switch on/off, 1-second, alarm, or power fail interrupt), the system transfers control to the corresponding interrupt servicing routine. The interrupt servicing routine to be started is determined from the status information in INTFG (0F4D5H) and the table TBL7508 at 0EFDEH.

The status of 1-second and alarm interrupt processing is stored in FG7508 at 0F4D7H.

The work areas related to 7508 interrupt processing are given below.

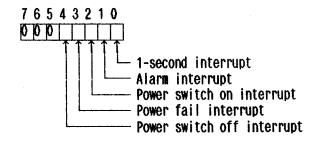

INTFG ( $\emptyset$ F4D5H) 1 byte Indicates the type of 7508 interrupt processing performed by the system. INTFG is set to  $\emptyset$ ØH when key interrupt processing is performed.

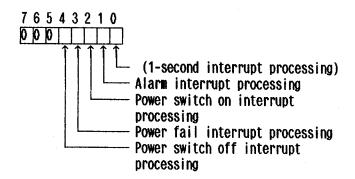

0

T

A 1 in a bit position indicates that the corresponding interrupt occurred.

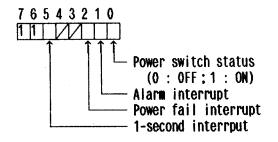

STS 7508 (0F4D6H) 1 byte Contains the status read by the system from the 7508 when a 7508 interrupt occurred. Values greater than or equal to 00H and smaller than or equal to 0BFH identify key interrupts and represent keys' hard codes. When STS 7508 contains a value greater than or equal to 0C0H:

A 1 in a bit position indicates that the corresponding interrupt occurred.

FG7508 (0F4D7H) 1 byte Is the 7508 interrupt processing flag.

A  ${\bf l}$  in a bit position indicates that the corresponding interrupt occurred.

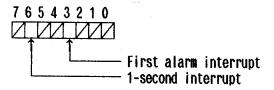

TBL7508 (ØEFDEH) 16 bytes

Is the table used to determine the 7508 interrupt processing to be serviced. Each byte has the following format:

A 1 in a bit position indicates that the corresponding interrupt occurred.

The meaning of the table entries are listed below.

| Address   | 7508 status | PW switch | initial |

|-----------|-------------|-----------|---------|

| Audi 699  | 1500 Status | status    | value   |

| EFDEH     | COH or EOH  | OFF       | 00H     |

| DF        |             | ON        | 10H     |

| EO        | C1H or E1H  | OFF       | 04H     |

| E1        |             | ON        | OOH     |

| E2        | C2H or E2H  | OFF       | 02H     |

| E3        |             | ON        | 12H     |

| <b>E4</b> | C3H or E3H  | 0FF       | 04H     |

| E5        |             | ON        | 02H     |

| E6        | C4H or E4H  | 0FF       | 08H     |

| E7        |             | ON        | 10H     |

| E8        | C5H or E5H  | 0FF       | 08H     |

| E9        |             | ON        | 08H     |

| EA        | C6H or E6H  | OFF       | 08H     |

| EB        |             | ON        | 10H     |

| EC        | C7H or E7H  | OFF       | 08H     |

| ED        |             | ON        | 08H     |

The presence or absence of the 1-second interrupt processing routine can be determined by software after rewriting the table.

## 4.7.4.4 Key interrupt processing

When an interrupt is generated by the 7508, the system issues a Status Read command (02H) to the 7508 to read the 7508 status. A status value 0BFH or smaller indicates that a key interrupt occurred and it is processed as such.

When a key interrupt is generated by the 7508, the system interprets the status data as a hard code which indicates the position of the key on the keyboard matrix. The key interrupt processing routine places the key's hard code into the key buffer (KBUF). If the key buffer is full, the key code is discarded.

If the hard code received from the 7508 is the one for the STOP key (10H for the standard keyboard and 0B6H for the item keyboard), the system performs special processing different from that for ordinary keys.

See Section 3.5, "Keyboard" for the key buffer and hard codes.

#### (1) STOP key special processing

Interrupt processing proceeds as follows when the system receives a hard code for the STOP key from the 7508:

- a) Sends a Keyboard Clear command to the 7508 to clear the 7-byte buffer of the 7508, and waits for approximately 40 ms (key scan time). If an item keyboard is installed or the STOP and CTRL/STOP keys are disabled (specified in ISYSREG (0F01EH)), the system does no special processing but carries out normal key interrupt processing.

- b) Reads the 7508 buffer to check whether the current key is pressed with the SHIFT key.

- c) Loads ØFFH into the BRKFLG (ØFØ19H) flag that indicates that the STOP key has been pressed.

- d) If the CTRL key is also pressed, the system loads 01H into CSTOPFLG (0F01AH), which is a flag indicating that the CTRL and STOP keys have been pressed simultaneously, CSTOPMCT (0F01BH), and CSTOPPRN (0F309H). The system bypasses this step if an item keyboard is installed or the CTRL and STOP keys are disabled.

- e) Checks the state of the switch key that is currently being pressed to determine the keyboard state.

- f) Clears the key buffer (KBUF) and loads the hard code (10H) for the STOP key into the key buffer. The system places 10H into the key buffer also when an item keyboard is installed.

The work areas related to key interrupt processing are described below.

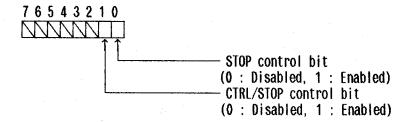

ISYSREG (ØFØ1EH) l byte Is the system function flag.

BRKFLG (ØFØ19H) 1 byte

Indicates whether the STOP key has been pressed.

- = 00H: The STOP key has not been pressed.

- = ØFFH: The STOP key has been pressed.

CSTOPFLG (ØFØlAH) 1 byte

Indicates whether the CTRL/STOP keys have been pressed.

- = 00H: The CTRL/STOP keys have not been pressed.

- = 01H: The CTRL/STOP keys have been pressed.

CSTOPMCT (ØFØ1BH) 1 byte

Flag for terminating microcassette processing.

- = 00H: The CTRL/STOP keys have not been pressed.

- = 01H: The CTRL/STOP keys have been pressed.

CSTOPPRN (ØF3Ø9H) 1 byte

Flag for terminating cartridge printer.

- = 00H: The CTRL/STOP keys have not been pressed.

- = 01H: The CTRL/STOP keys have been pressed.

Note: BRKFLG and CSTOPFLG are reset to 00H when BIOS CONIN or CONST is called and CSTOPMCT and CSTOPPRN are reset by PSTBIOS.

# 4.7.4.5 1-second interrupt processing

1-second interrupt processing proceeds as follows:

- Increments 16-bit timer TIMERØ (ØEF8FH) by 1.

- b)

- Decrements 16-bit timer TIMER1 (ØEF91H) by 1. Processes timer function TMFUNC (ØF313H). C) When TMFUNC (0F313H) contains a nonzero value, the interrupt processing routine decrements TMSEC (@F4DAH) by 1. If the TMSEC reaches 00H as the result of the decrement, the interrupt processing routine sets TMFUNG to 00H and TMGLAG (ØF314H) to ØFFH.

- d) Counts down the ROM cartridge power-off time.

- Counts down the alarm repeat time. e)

The areas referred to in steps a), b), and c) are 1-second counters available for application programs and those referred to in steps d) and e) are counters available for system control. TIMERØ is also used by the system to monitor the auto power-off time.

- (1) Uses of TIMERØ and TIMER1 TIMERØ and TIMER1 are 16-bit 1-second counters and incremented or decremented by 1 every time a 1-second interrupt occurs. counters can be used as reference-only counters (not overwritten) to measure processing time.

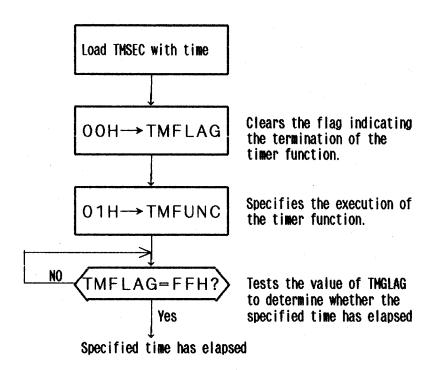

- (2) Use of TMFUNC TMFUNC is a flag area available for the user to specify the execution of the timer function for checking for the lapse of a specified time. Figure 4.7.10 shows how to use this flag.

Fig. 4.7.10 Using TMFUNC

The work areas related to 1-second interrupt processing are described below.

TIMERØ (ØEF8FH) 2 bytes 16-bit timer incremented by 1 every time a 1-second interrupt occurs.

TIMER1 (ØEF91H) 2 bytes 16-bit timer decremented by 1 every time a 1-second interrupt occurs.

TMFUNC (ØF313H) 1 byte Timer function flag.

- = 00H: The timer function is not specified.

- = Nonzero: The timer function is specified.

TMFLAG (ØF314H) 1 byte Timer flag.

When TMFUNC contains a nonzero value, TMSEC is decremented by 1 every 1-second interrupt and TMFLAG is set to ØFFH when TMSEC reaches 0000H.

TMSEC (ØF4DAH) 2 bytes Timer counter.

When TMFUNC contains a zero value, TMSEC is decremented by 1 every 1-second interrupt and when TMSEC reaches 0000H, TMFLAG is set to 0FFH and TMFUNC to 00H.

## 4.7.4.6 Alarm interrupt processing

An alarm interrupt occurs when the time specified by BIOS TIMDAT with a Set Alarm/Wake is reached. Alarm interrupts are distinguished from wake interrupts by software; on hardware, only alarm interrupts can occur.

Although the alarm time can be specified to the precision of month, day, day of the week, hour, minute, and second, the minimum unit is 10 seconds. This is because the 7508 recognizes the arrival of an alarm time by a coincidence between the counter value and the specified time in the precision up to 10 seconds. Accordingly, once the set alarm time is reached, a maximum of 10 alarm interrupts can occur. PINE OS takes one of the 10 interrupts as a true alarm interrupt.

PINE OS places hooks in the alarm interrupt processing routine so that the application programs can extend the capability of the alarm interrupt processing routine. See Section 4.3, "Hooks" for details on alarm hooks.

The display of the alarm screen can be disabled by software during alarm processing using ALRMDS ( $\emptyset$ EFF1H).

#### 4.7.4.7 Power switch on interrupt processing

A power switch on interrupt occurs when the power switch is switched from the OFF to ON position. The power switch on processing routine only sets the power switch on flag PWSWONFG (0F4DCH). See Section 2.4, "Power-on" for power-on processing started when the main power is off.

The work area related to power switch on interrupt processing is described below.

PWSWONFG (0F4DCH) 1 byte Power switch on flag.

- = 00H: No power switch on interrupt has occurred.

- = ØFFH: A power switch on interrupt has occurred. Reset to ØØH when power switch on processing is started with the main power switch in the OFF position.

## 4.7.4.8 Power fail interrupt processing

A power fail interrupt occurs when the main battery voltage falls below a certain level. The threshold level is 4.8 volts for NiCd batteries and 4.0 volts for Mn dry batteries.

When a power fail interrupt occurs, the corresponding interrupt processing routine sets the power fail flag BTRYFG (ØEFEEH) to alert that the battery voltage has been fallen. See Section 2.6, "Power Fail" for details on the power fail screen.

Once a power fail interrupt occurs, the same interrupt occurs every one second. If main power is not shut down within 50 seconds after the first power fail interrupt, the 7508 forces main power to be shut down.

The work area related to power fail interrupt processing is described below.

BTRYFG (ØEFEEH) l byte Power fail interrupt flag.

- = 00H: No power fail interrupt has occurred.

- =  $\emptyset$ FFH: A power fail interrupt has occurred. Reset to  $\emptyset$  $\emptyset$ H by a power-on start sequence.

## 4.7.4.9 Power switch off interrupt processing

A power switch off interrupt occurs when the power switch is switched from the ON to OFF position. The power switch off processing routine tests the current key shift state to determine whether the CTRL key has been pressed, places the result into power switch off flag PWSWOFFG (0F4DDH), then turns off power.

The key shift state that determines the continue or restart mode power-off can be altered. A continue mode power-off occurs when the value of CNTNKEY (ØEF2AH) match the key shift state when the power switch off interrupt occurred. See Section 2.5, "Power-off" for details on power off processing.

The work areas related to power switch off interrupt processing are described below.

Е

4

Ι

r

V

W

PWSWOFFG (ØF4DDH) 1 byte Power switch off flag.

- = 00H: No power switch off interrupt has occurred.

- = 01H: A restart mode power switch off interrupt

occurred.

= 02H: A continue mode power switch off interrupt has occurred.

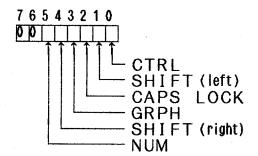

CNTNKEY ( $\emptyset$ EF2AH) 1 byte Continue key shift state flag.

A l in a bit position indicates that the corresponding shift key is pressed.

Only bit  $\emptyset$  (CTRL) is valid when an item keyboard is installed. Only continue mode power switch off interrupts are enabled when CNTNKEY contains  $\emptyset\emptyset$ H, irrespective of the key shift state. This area is initialized to  $\emptyset$ lH.

#### 4.7.5 ART Interrupts

An ART interrupt occurs when the RxRDY pin in the ART block is set. ART interrupt processing proceeds as follows (see also Section 3.4, "BIOS Details" since ART interrupt processing is closely related to BIOS RSIOX processing):

- a) Does nothing if the RSIOX OPEN function has not been performed.

- b) Checks for errors (framing, receive overrun, parity, and receive buffer overflow errors).

- c) Reads the received data into the receive buffer.

- d) If XON/XOFF control is specified, checks the number of the received bytes in the receive buffer and sends an XOFF code if it exceeds the 3/4 of the buffer size.

#### 4.7.6 OVF Interrupts

An OVF interrupt occurs when an FRC (Free Running Counter) overflow occurs. The FRC is a 16-bit counter running on the 616.6 kHz clock, so an OVF interrupt occurs every 106.7 msec or so.

PINE OS uses OVF interrupts for controlling cursor blinking. The cursor turns on and off every 500 msec or so. The blinking interval can be changed by rewriting BLNKTIME (ØEFBAH).

BLNKTIME (ØEFBAH) 1 byte Specifies the cursor blink time in 100 ms units. This area is initialized to 04H.

#### 4.7.7 ICF/EXT Interrupts

ICF interrupts occur as the state of the input to the barcode reader or external cassette drive changes whereas EXT interrupts are generated by the interrupt signal from external devices (sent via the system bus).

When an ICF or EXT interrupt occurs, the PINE does nothing but sets interrupt flag INTTYPE at ØEFD3H. Hooks are provided for extension of ICF/EXT interrupt processing. See Section 4.3, "Hooks" for details.