### MINC-11

# Book 7: Working with MINC Devices

#### November 1978

This document describes the physical and electrical characteristics of MINC systems and provides information about making laboratory/MINC connections, system reconfiguration, and troubleshooting.

Order Number AA-D572A-TC

MINC-11

VERSION 1.0

To order additional copies of this document, contact the Software Distribution Center, Digital Equipment Corporation, Maynard, Massachusetts 01754

digital equipment corporation · maynard, massachusetts

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license and may only be used or copied in accordance with the terms of such license.

No responsibility is assumed for the use or reliability of software on equipment that is not supplied by DIGITAL or its affiliated companies.

Copyright (C) 1978 by Digital Equipment Corporation

The postage-prepaid READER'S COMMENTS form on the last page of this document requests the user's critical evaluation to assist us in preparing future documentation.

The following are trademarks of Digital Equipment Corporation:

DIGITAL DECsystem-10 **MASSBUS OMNIBUS DECtape** DEC DIBOL **OS/8** PDP PHA **EDUSYSTEM** DECUS FLIP CHIP **UNIBUS RSTS COMPUTER LABS** FOCAL RSX **INDAC TYPESET-8** COMTEX DDT LAB-8 TYPESET-11 **TMS-11** DECCOMM DECSYSTEM-20 ITPS-10 ASSIST-11 RTS-8 MINC-11 DECSYSTEM-2020

#### **CONTENTS**

#### Record Keeping Aids xiv SYSTEM HARDWARE xv PART 1 DATA ACQUISITION AND CONTROL CHAPTER 1 THE MINC DATA TRANSFER SYSTEM 1 MODULE PLACEMENT 1 MINC FUNCTION DIAGRAMS 2 MINC CONNECTOR BLOCKS 4 CHAPTER 2 ANALOG-TO-DIGITAL CONVERSION 7 APPLICABLE LAB MODULE ROUTINES 7 ANALOG-TO-DIGITAL CONVERTER 7 Front Panel Controls 8 Mode Indicators 9 Expansion 9 Preamplified Inputs 9 Initiation of A/D Conversions 10 Connector Block Labeling 10 PREAMPLIFIER 11 Front Panel Controls 11 Configuration with A/D or Multiplexer 12 When a Preamplifier Is Required 14 Connector Block Labeling 14 DUAL MULTIPLEXER 14 Front Panel Indicators 14

Relationship to Other MINC Documents xiii

INTRODUCTION xiii

USE OF THIS MANUAL xiii

Glossary Flags (\*) xiv

#### **CONTENTS**

| Configuration with A/D and Preamplifier 15<br>When Multiplexers Are Required 15<br>Connector Block Labeling 17<br>CLOCK MODULE 22                                                                                                                                                                                                                                                                       |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Configuration with A/D Converter 22 ANALOG INPUT CONNECTIONS 22 Connecting Grounded Apparatus 22 Connecting Floating Devices to the A/D Group 23 Single-ended Selection Straps 24                                                                                                                                                                                                                       |    |

| Input Selection (Channels 0-3) 25 CONTROL SETTINGS AND CONNECTIONS 26                                                                                                                                                                                                                                                                                                                                   |    |

| CHAPTER 3 TIME INTERVAL CONTROL AND SAMPLING MINC TIME-KEEPING MODES 29 MINC CLOCK 30 Schmitt Triggers 32 The MINC Clock Connector Block 32 Control Settings and Connections 33                                                                                                                                                                                                                         | :9 |

| CHAPTER 4 DIGITAL-TO-ANALOG CONVERSION 37  DIGITAL-TO-ANALOG CONVERTER 37  D/A Input/Output Relationships 38  Minimum Voltage Increments 39  Expansion 40  DAC 3 Resolution 41  Connector Block 42  D/A CONNECTIONS TO EXTERNAL DEVICES 43  Grounded Devices 43  Floating Devices 44  Oscilloscopes and X-Y Plotters 44                                                                                 |    |

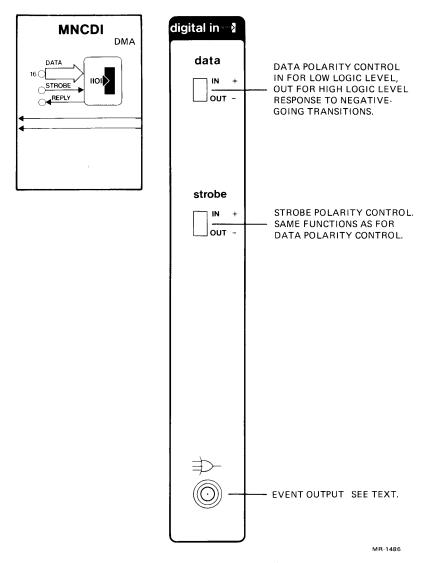

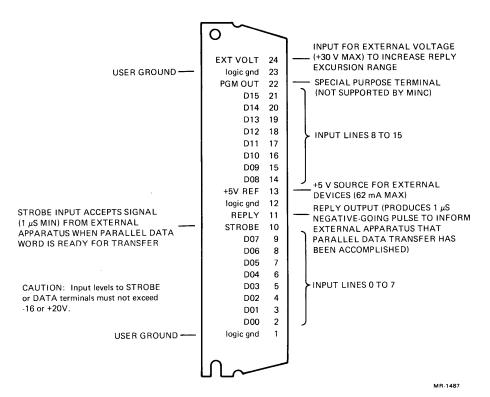

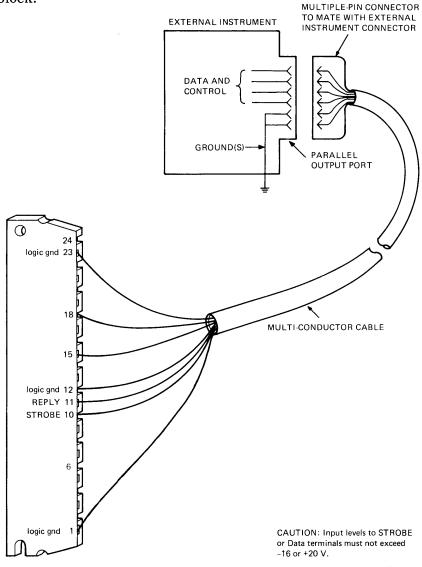

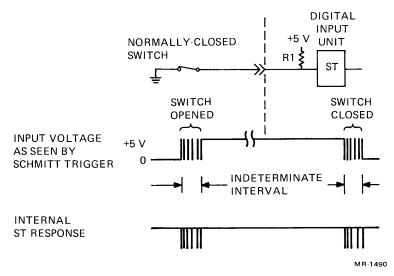

| CHAPTER 5 DIGITAL INPUT AND OUTPUT 47  THE MINC DIGITAL INPUT MODULE 47  Expansion 48  Connections to External Parallel Data Ports 49  Data Latching and Polarity 51  Digital Input Connections from External Switches 51  THE MINC DIGITAL OUTPUT MODULE 54  Expansion 54  Connections to External Parallel Data Port 55  Transfers Requiring Non-TTL* Voltages 56  Driving Power-consuming Devices 58 |    |

| CHAPTER 6 USING THE IEEE INSTRUMENT BUS 61 IEEE BUS 61 BUS PROTOCOL 61 Talkers 62                                                                                                                                                                                                                                                                                                                       |    |

Listeners 63

Controllers 63

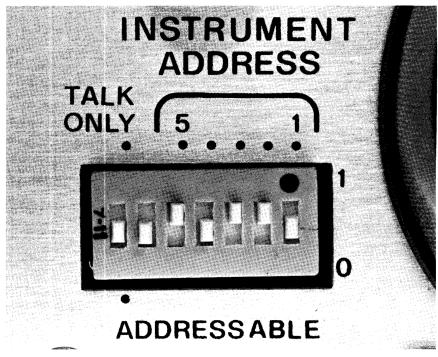

ADDRESSING 63

Setting Instrument Addresses 63

Primary Address Switch Arrays 63

Addressable Mode 64

Recording Instrument Addresses 64

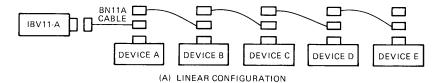

CONNECTING BUS CABLES 64

Maximum System Cable Length 65

#### CHAPTER 7 CONNECTING SERIAL ASCII APPARATUS 67

#### PART 2 SPECIFICATIONS, CONFIGURATION, TROUBLE-SHOOTING

#### **CHAPTER 8 MINC SYSTEM SPECIFICATIONS 71**

SYSTEM ENVIRONMENTAL REQUIREMENTS 71

DETAILED SPECIFICATIONS: STANDARD MINC ITEMS 71

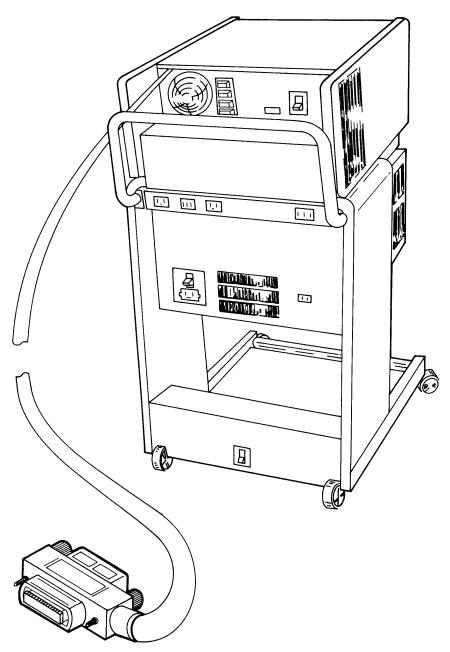

MINC Cart, with Standard MINC System Components 71

Dual Diskette Drive (RXO2M) 72

MINC Chassis (MNCBA) 73

Processor (KD11-HA) 73

IEEE Instrument Bus Interface (IBV11-A) 73

Memory (MSV11-DD) 74

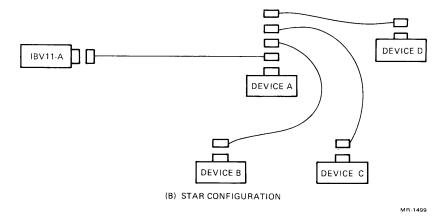

Serial ASCII Interface (DLV11-J) 74

Diagnostic Bootstrap/Terminator (BDV11-AA) 74

Keyboard/Monitor with Graphics Display (VT105) 75

DETAILED SPECIFICATIONS: OPTIONAL MINC ITEMS 77

A/D Converter (MNCAD) 77

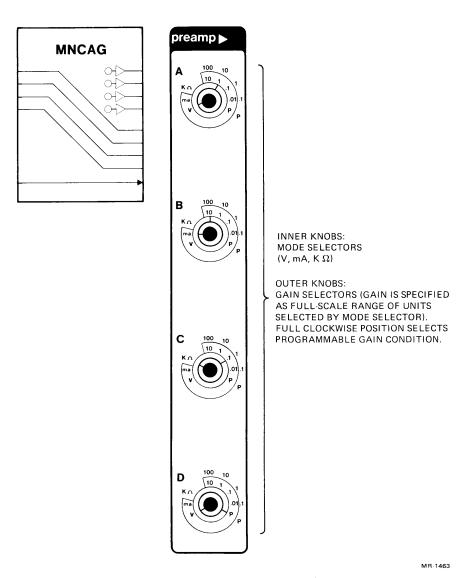

MINC Preamplifier (MNCAG) 77

MINC Dual Multiplexer (MNCAM) 78

MINC Clock (MNCKW) 78

MINC D/A Converter (MNCAA) 79

MINC Digital Input Unit (MNCDI) 80

MINC Digital Output Unit (MNCDO) 81

#### CHAPTER 9 SYSTEM CONFIGURATION PROCEDURES 83

SYSTEM EXPANSION 83

Module Placement Sequence 84

CHANGING OPERATING MODES ON THE MINC

TERMINAL 85

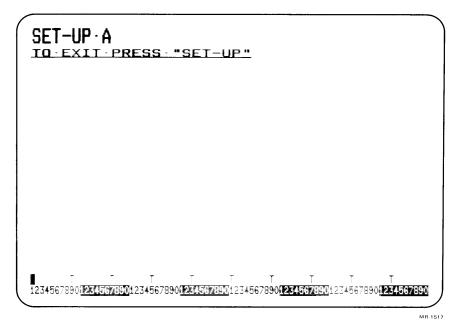

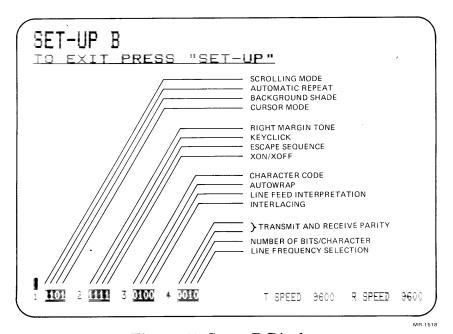

How to Use Setup Mode 86

Setup A 86

Setup B 89

## CHAPTER 10 CONNECTIONS TO EXTERNAL APPARATUS 93

USING THE MINC CONNECTOR BLOCKS 93

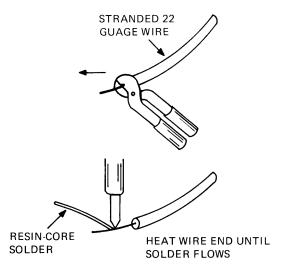

Wire Preparation 93

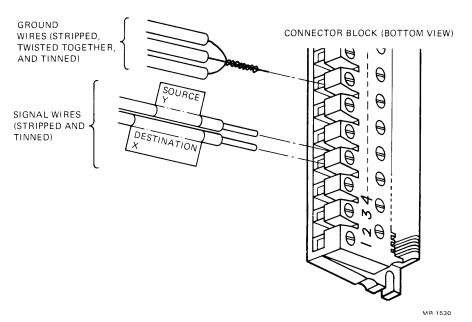

Wire Installation 94

#### **CONTENTS**

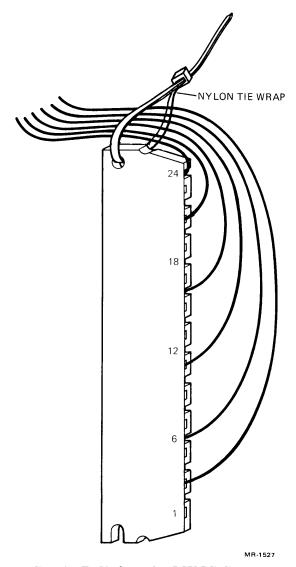

Strain Relief 94

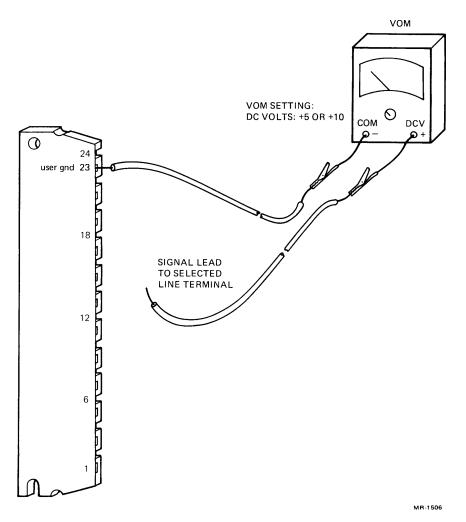

CONFIRMING DATA TRANSFER CONNECTIONS 94

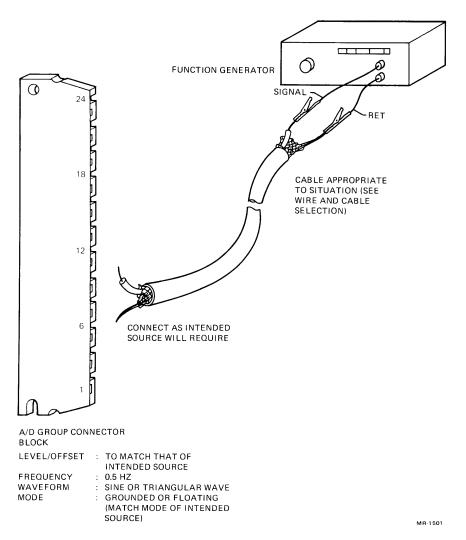

Running Connection Confirmation Programs 96

A/D Group Inputs 96

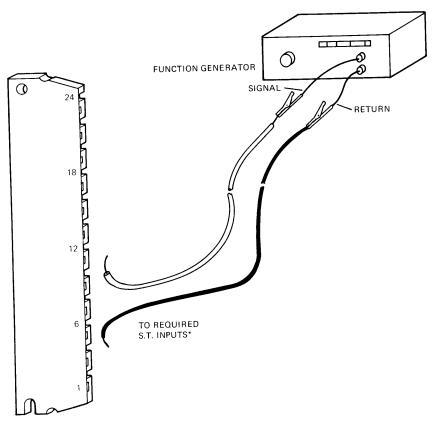

Clock Schmitt Trigger Inputs 98

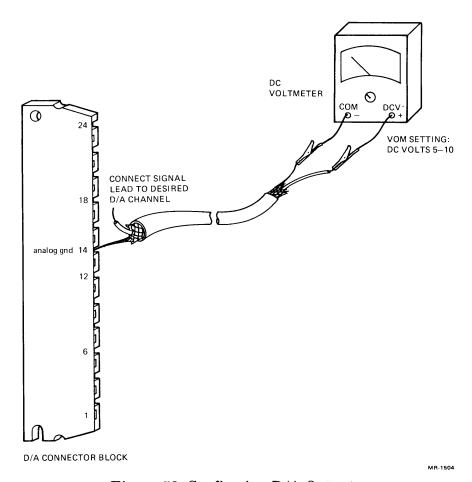

D/A Outputs 100

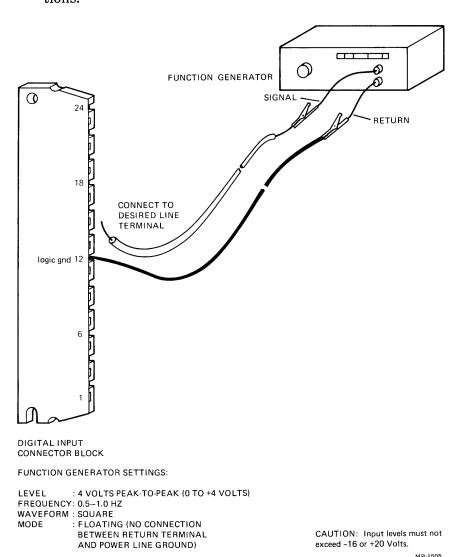

Signals to Digital Input Units 101

Signals from Digital Output Units 102

MAPPING LAB MODULE CONNECTIONS 104

#### **CHAPTER 11 NOISE IN ANALOG TRANSMISSIONS 109**

ELECTROSTATIC NOISE 110

MAGNETIC NOISE 111

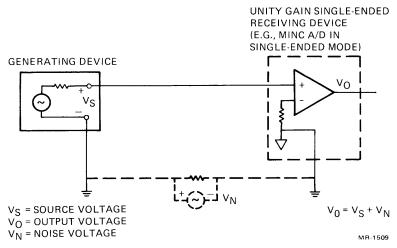

COMMON MODE (GROUND LOOP) NOISE 112

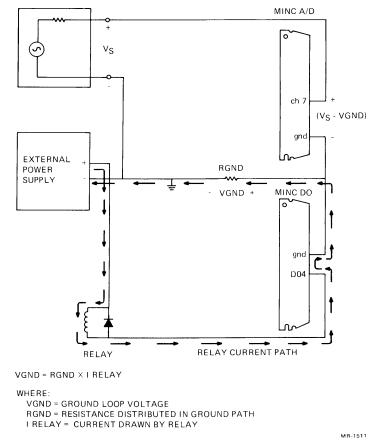

Ground Loops 113

CROSSTALK NOISE 115

MULTIPLEXER NOISE 116

RESIDUAL NOISE IN A/D CONVERSIONS 116

#### **CHAPTER 12 PREVENTIVE MAINTENANCE 119**

#### CHAPTER 13 MINC SYSTEM TROUBLESHOOTING 121

AIDS TO HARDWARE FAULT DIAGNOSIS 122 TROUBLESHOOTING PROCEDURE 123 RUNNING DIAGNOSTICS 126

#### **GLOSSARY OF MINC TERMS 133**

**INDEX** 145

**FIGURES**

| Figure | 1.  | MINC Laboratory Module (A/D Converter) 2                   | FIGURE |

|--------|-----|------------------------------------------------------------|--------|

|        | 2.  | MINC Function Diagrams in a Typical                        |        |

|        |     | Configuration 3                                            |        |

|        | 3.  | MINC Connector Block 4                                     |        |

|        | 4.  | MINC A/D Converter 8                                       |        |

|        | 5.  | MINC A/D Connector Block 10                                |        |

|        | 6.  | MINC Preamplifer 11                                        |        |

|        | 7.  | Signal Routing — Preamplifier to A/D 13                    |        |

|        | 8.  | Signal Routing — Preamplifier to                           |        |

|        |     | Multiplexer 13                                             |        |

|        | 9.  | MINC Preamplifer Connector Block 15                        |        |

|        | 10. | The MINC Dual Multiplexer 16                               |        |

|        | 11. | Maximum Expansion of Single-Ended A/D                      |        |

|        |     | Channels 17                                                |        |

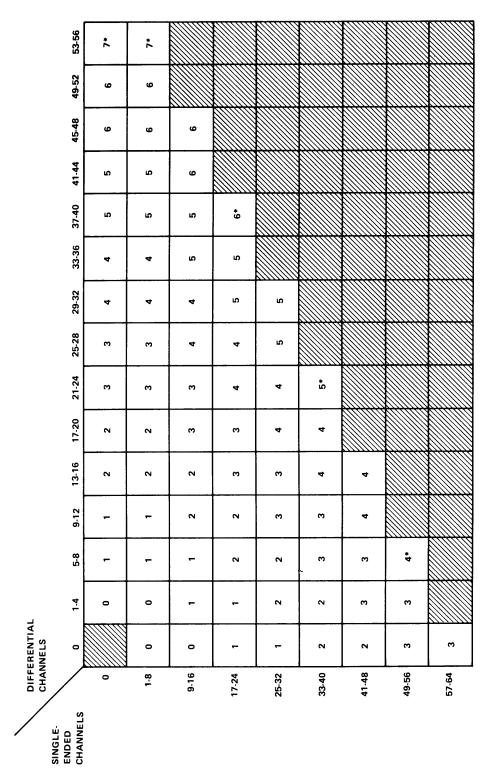

|        | 12. | Maximum Expansion of Unpreamplified                        |        |

|        |     | Differential A/D Channels (8 Single-Ended, 56              |        |

|        |     | Differential) 18                                           |        |

|        | 13. | Maximum Expansion of Preamplified                          |        |

|        |     | Differential A/D Channels (20 Differential, 8              |        |

|        |     | Single-Ended) 19                                           |        |

|        |     | Dual Multiplexer Connector Block Labeling 21               |        |

|        | 15. | Single-Ended* Connections to MINC A/D Group                |        |

|        |     | from Grounded Sources 23                                   |        |

|        | 16. | Differential* Connections to MINC A/D Group                |        |

|        |     | from Grounded Sources 24                                   |        |

|        | 17. | Single-Ended Connections to MINC A/D Group                 |        |

|        | 10  | from Floating Sources 25                                   |        |

|        | 18. | Single-Ended Selector Straps 26                            |        |

|        | 19. | The MINC Clock 30                                          |        |

|        | 20. | Schmitt Trigger Operation 31                               |        |

|        | 21. | •                                                          |        |

|        | 22. | MINC Clock Connector Block 33                              |        |

|        | 23. | MINC Clock—ST1 and ST2 Connections and                     |        |

|        | 0.4 | Control 34                                                 |        |

|        | 24. | The MINC D/A Converter 38 Channel 2 Control Pit Outputs 20 |        |

|        | 25. | Channel 3 Control Bit Outputs 39                           |        |

|        | 26. | MINC D/A Connector Block 41                                |        |

|        | 27. | D/A Connections to a Grounded Device 42                    |        |

|        | 28. | D/A Connections to a Floating Device 43                    |        |

|        | 29. | MINC D/A Connected to Scope with Differential              |        |

|        |     | X and Y Inputs 44                                          |        |

#### **CONTENTS**

|             | Single-Ended Inputs 45                                                              |

|-------------|-------------------------------------------------------------------------------------|

| 31.         | MINC D/A Connected to X-Y Plotter 46                                                |

| 32.         |                                                                                     |

| 33.         | MINC Digital Input Connector Block 49                                               |

| 34.         | Connections Between Digital Input Unit and                                          |

|             | External Instrument with Parallel Output                                            |

|             | Port 50                                                                             |

| 35.         | Timing Relationships for Data Transfer to                                           |

|             | Digital Input from External Parallel-transfer                                       |

|             | Instrument 51                                                                       |

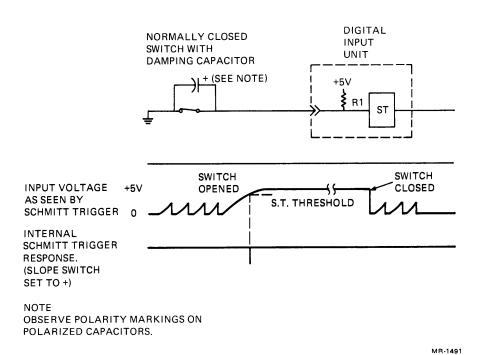

| 36.         | The Effects of Contact Bounce on a Digital in                                       |

|             | Schmitt Trigger 52                                                                  |

| 37.         | Capacitive Contact Debouncing for a Digital                                         |

|             | Input Unit Schmitt Trigger 53                                                       |

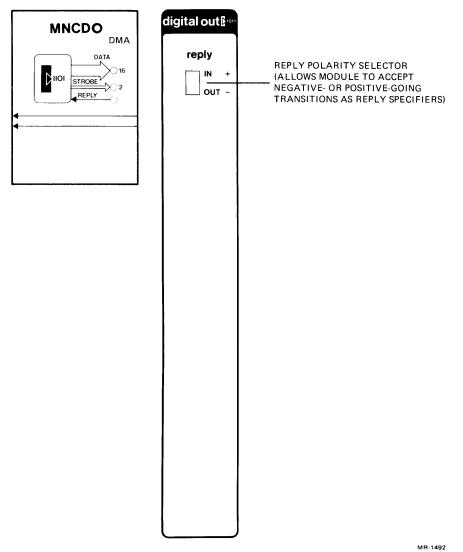

| 38.         | MINC Digital Output Module 55                                                       |

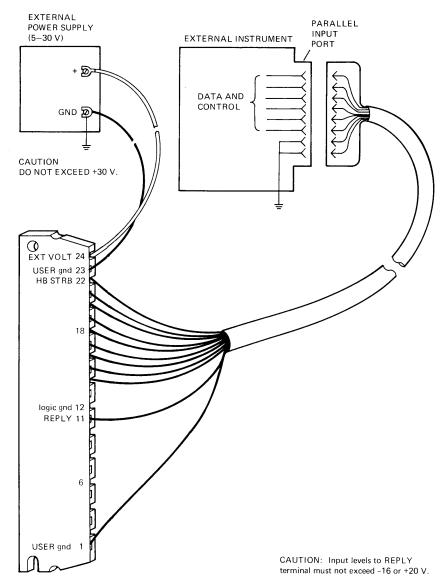

| 39.         | MINC Digital Output Connector Block 56                                              |

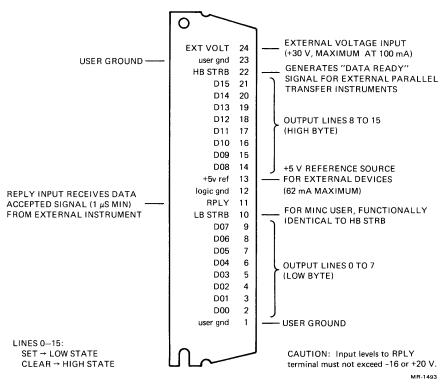

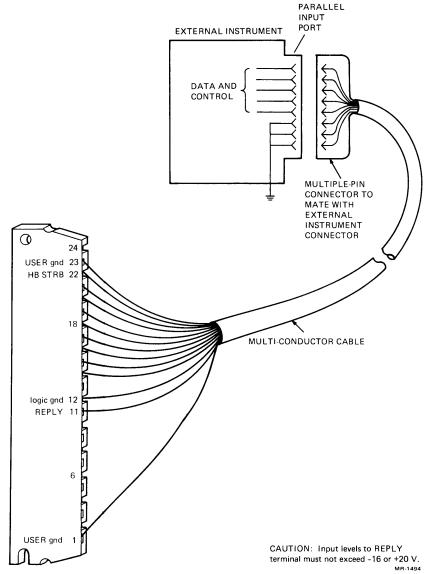

| 40.         | Connections to External Instrument with TTL-                                        |

|             | compatible Parallel Data Port 57                                                    |

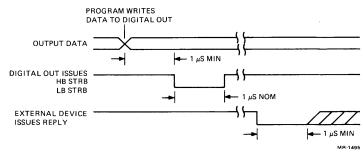

| 41.         | Timing of Parallel Data Transfer from the                                           |

|             | Digital Output to External Apparatus 57                                             |

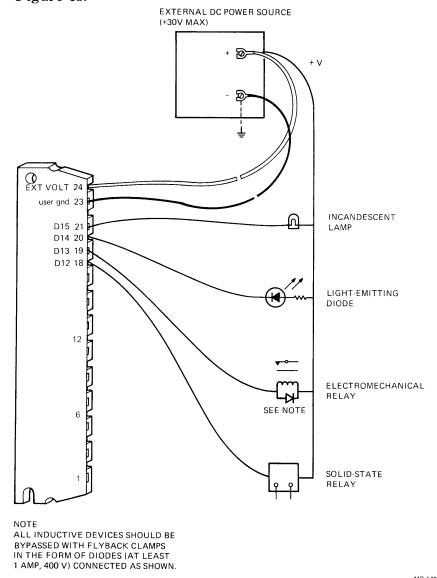

| 42.         | Use of the EXT VOLT Terminal 58                                                     |

| 43.         | Connecting Discrete External Devices to the                                         |

|             | MINC Digital Output 59                                                              |

| 44.         | IEEE Bus Cable 62                                                                   |

| 45.         | Typical Talk/Listen Address Switch 64                                               |

| 46.         | Bus Cable Connections 66                                                            |

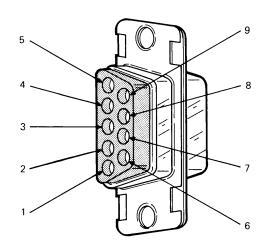

| 47.         | Serial Line Unit (SLU) Ports 68                                                     |

| 48.         | Wiring the SLU Connector 68                                                         |

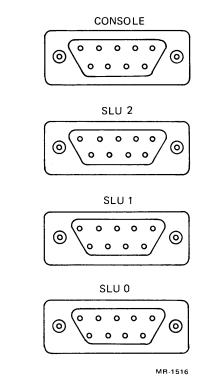

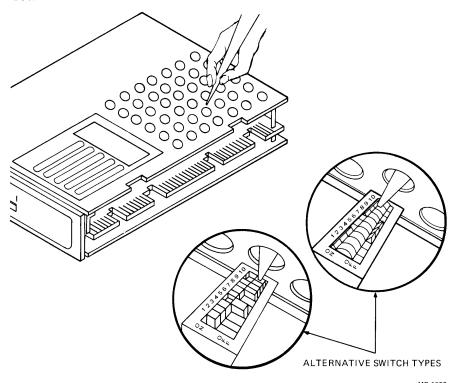

| <b>49</b> . | Setting Module I.D. Switches 84                                                     |

| 50.         | Setup A Display 86                                                                  |

| 51.         | Setup B Display 89                                                                  |

| 52.         | Preparing Wire for MINC Connector Blocks 93                                         |

| 53.         | Installing Wires in MINC Connector Block 94                                         |

| 54.<br>55.  | Strain Relief on the MINC Connector Block 95                                        |

|             | Confirming A/D-group Inputs 97<br>ADCON Display 98                                  |

| 56.<br>57.  |                                                                                     |

| 57.<br>58.  | Confirming Schmitt Trigger Inputs 99 Confirming D/A Outputs 100                     |

| 59.         | Confirming Digital Input Connections 102                                            |

| 60.         | Confirming Digital Input Connections 102  Confirming Digital Output Connections 103 |

| 61.         | Use of Shielded Lead to Reduce Electrostatic                                        |

| 01.         | Noise Pickup 110                                                                    |

| 62.         | Use of Twisted Pair Leads to Reduce Magnetic                                        |

| 02.         | Noise Pickup 112                                                                    |

| 63.         | Common Mode Noise Pickup 113                                                        |

| 64.         | Typical Ground Loop Conditions 114                                                  |

| 04.         | Typical Ground Loop Conditions 114                                                  |

Figure 30. MINC D/A Connected to Scope with Grounded

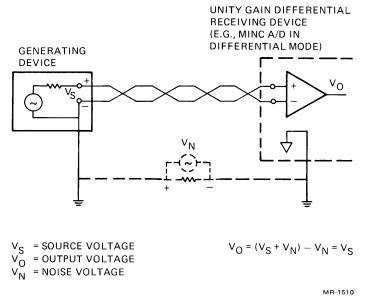

| Figure 65. | Common Mode Noise Voltages Input to a           |

|------------|-------------------------------------------------|

| _          | Differential Device 115                         |

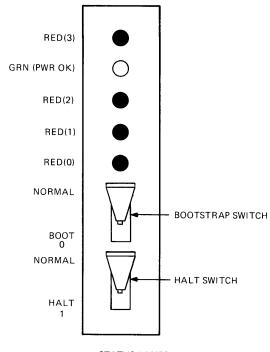

| 66.        | BDV11 Diagnostic Lamps 123                      |

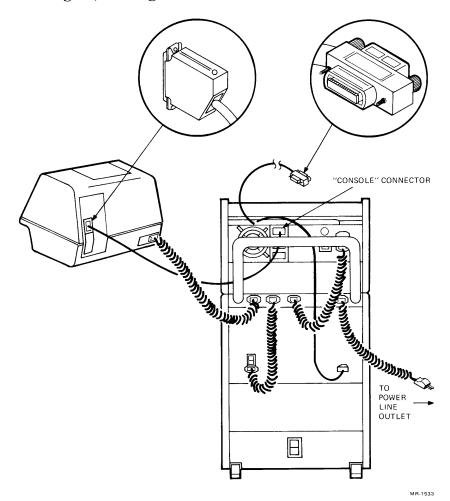

| 67.        | MINC Cable Connections 124                      |

| 68.        | MINC Switches 125                               |

| 69.        | Terminal Response to "Break" Key                |

|            | Operation 126                                   |

| 70.        | SLU Test Connector 127                          |

| 71.        | Initial Display from the MINC Diagnostic        |

|            | Diskette 127                                    |

| 72.        | Operating Instructions Issued by the Diagnostic |

|            | Chain 128                                       |

| 73.        | Typical Error Identification 129                |

| 74.        | Typical Error-free Run of the MINC 11           |

|            | Diagnostic Chain 130                            |

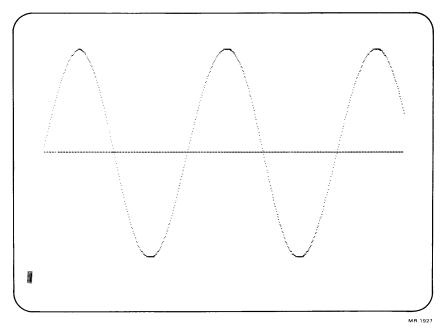

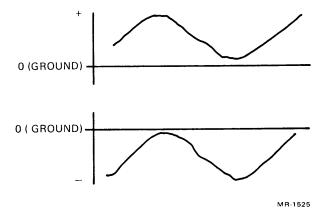

| 75.        | Bipolar Voltage Waveform 134                    |

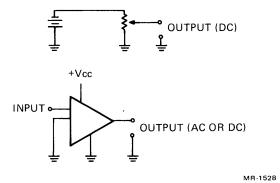

| 76.        | Bipolar Output Devices 134                      |

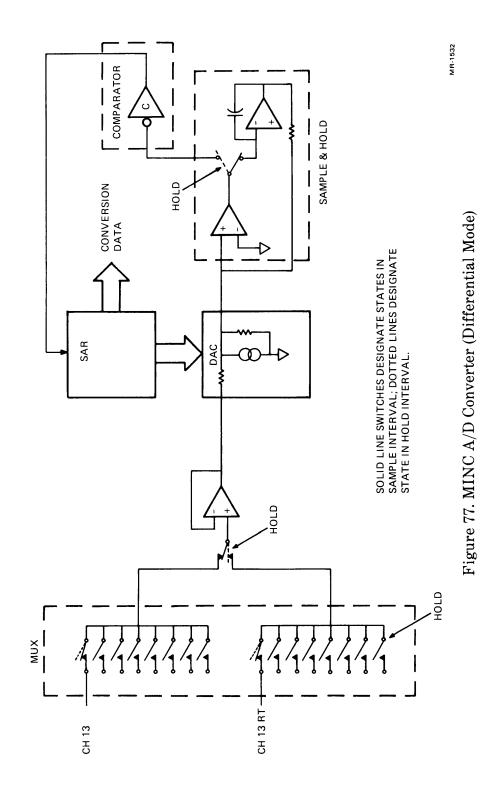

| 77.        | MINC A/D Converter (Differential Mode) 136      |

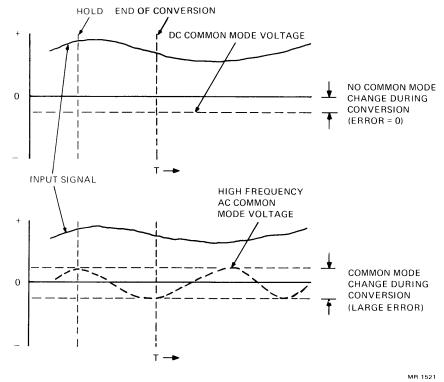

| 78.        | DC vs. AC Common Mode Voltages into the         |

|            | MINC A/D 137                                    |

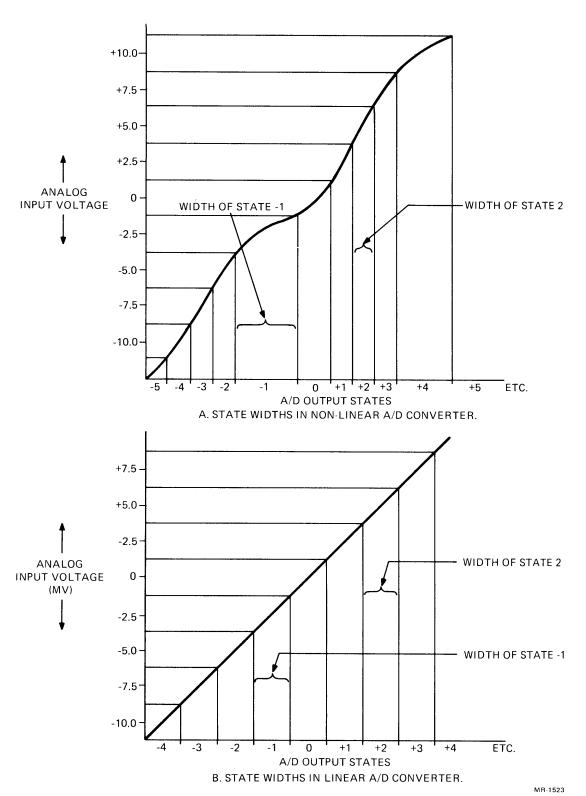

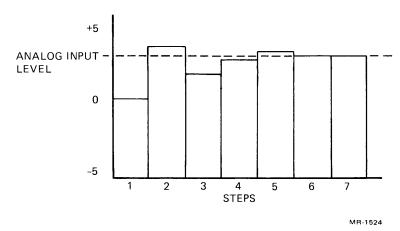

| 79.        | State Width in A/D Conversions 141              |

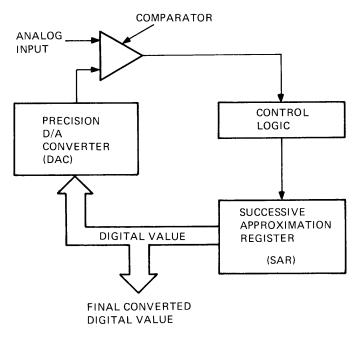

| 80.        | Successive Approximation Block Diagram 142      |

| 81.        | Progression of Levels in Successive             |

|            | Approximation DAC (7 bits only) 143             |

| 82.        | Unipolar Voltage Waveforms 144                  |

| 83.        | Unipolar Output Devices 144                     |

i

|    | 1. MINC Module Option Designation Codes 5           | TABLES |

|----|-----------------------------------------------------|--------|

|    | 2. Preamplifier Mode/Range Relationships 12         |        |

|    | 3. Multiplexers Required to Support One A/D with n  |        |

|    | Differential and x Single-ended Input               |        |

|    | Channels 20                                         |        |

| 4  | 4. Connections and Control Settings for A/D         |        |

|    | Conversion Routines 27                              |        |

| Į. | 5. Connections and Control Settings for MINC Clock  |        |

|    | Routines 35                                         |        |

| (  | 3. Connections and Control Settings for             |        |

|    | Timestamping and Elapsed Time Routines 36           |        |

|    | 7. MINC D/A Data/Voltage Relationships 40           |        |

|    | 8. Minimum D/A Voltage Increments 40                |        |

|    | 9. Delay Intervals for Debouncing Capacitors as     |        |

|    | Shown in Figure 37 53                               |        |

| 10 | ). Connections and Control Settings Required by the |        |

|    | DIN Routine 54                                      |        |

| 1  | L. Connections and Control Settings Required by the |        |

|    | DOUT Routine 60                                     |        |

| 15 | 2. Talk/Listen Address Switch Settings 65           |        |

| 13 | 3. Input/Output Characteristics of SLU's 0, 1, and  |        |

|    | 2 67                                                |        |

| 14 | 4. Maximum Number of Addressable MINC               |        |

|    | Modules 84                                          |        |

| 1  | 5. MINC Module Placement Sequence 85                |        |

|    | 3. Diagnostic Programs in the MINC 11 Chain 128     |        |

i

#### INTRODUCTION

MINC is an integrated system for manipulating data and for monitoring and controlling complex external apparatus. Although computer-based, it is designed not to require detailed knowledge on your part regarding traditional computer hardware and software distinctions. Only at two points does this design principal not fully apply: when electrical connections are made between the MINC system and the outside world, and when system malfunction or operator error makes it necessary to isolate physical system components for scrutiny.

This manual is for users who must approach MINC as a physical and electrical object. It is organized in two parts. Part 1 concerns those questions likely to be asked by anyone who wishes to use MINC as a data transfer device—that is, to acquire data from or transmit data or control information to apparatus outside of the system. This section defines the electrical and mechanical preconditions for running the data transfer routines described in *Book 6: MINC Lab Module Programming*. Part 2 contains information pertinent to troubleshooting and diagnosing problems generated by the physical system or by operator error. It also contains recommendations for configuring systems with multiple MINC modules, setting up the system terminal, confirming data transfer connections, and reducing noise pickup.

**Relationship to Other MINC Documents.** This manual is not intended to be used alone, but to be read in conjunction with other MINC documents. The most important of these is *Book 6: MINC Lab Module Programming*, which describes the routines

USE OF THIS MANUAL

i

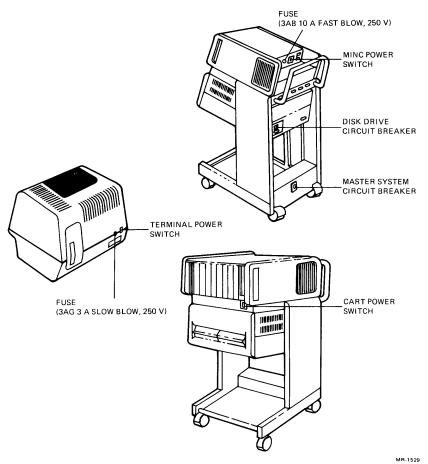

#### SYSTEM HARDWARE

The physical components of a MINC system can be grouped into two categories: items common to all MINC systems, and those that can be purchased as options, either when the system is first acquired or at some later time as add-ons. See Part 2 for detailed specifications of all components.

All MINC systems include the following standard items:

```

MINC cart, which provides support and transport for:

Dual diskette drive (RX02M)

MINC chassis (MNCBA) with power supply,

containing:

LSI-11 processor (KD11-NA)

32,768 words (65,536 8-bit bytes) of memory

(MSV11-DD)

Diskette drive interface (RXV21)

Four-channel serial ASCII interface (DLV11-J)

IEEE bus interface (IBV11-A)

Bus terminator/diagnostic/bootstrap module

(BDV11-AA)

Terminal with built-in graphics capability (VT105)

```

MINC systems can include some or all of the following lab modules:

Analog-to-digital converter (MNCAD)

Preamplifier (MNCAG)

Dual multiplexer (MNCAM)

Clock (MNCKW)

Digital-to-analog converter (MNCAA)

Digital input unit (MNCDI)

Digital output unit (MNCDO)

MINC systems can also include:

Dot-matrix printer (LA35)

Isolation transformer (MNCIT)

110 baud, 20 mA serial line interface (DLV11-KC)

that control the MINC lab modules and also provides a general framework for approaching control programming problems. Although *Working with MINC Devices* identifies the data transfer routines pertinent to each lab module, its coverage of these routines is cursory and is written on the assumption that the reader either has already read relevant portions of *Book 6* or will go to *Book 6* for the necessary background and specific details.

Similarly, Chapter 6 gives information about the IEEE instrument bus that will be essential to you if you use the routines described in *Book 5: MINC IEEE Bus Programming*. Chapter 9 gives information about the MINC terminal that will be of general use in all system operations and of specific use when you are writing routines of the sort described in *Book 4: MINC Graphic Programming*.

Glossary Flags (\*). Most technical terms used in this manual are defined when they are used. Definitions for a few terms, however, must be lengthy to be meaningful. These definitions are given in the Glossary at the end of the manual. When terms included in this Glossary are first used in the manual, they are followed by an asterisk (\*). If, when you encounter the asterisk, detailed knowledge of the word's meaning seems necessary to you, you can go to the Glossary definition. If you are reading a section for the first time, however, you will probably decide that you don't wish to be distracted by detail and choose to continue reading.

Detailed understanding of all terms used in this manual will ultimately help maximize your ability to exploit the MINC system's very considerable resources. However, the system lets you accomplish a great deal long before you have achieved such understanding. This system attribute, in fact, lies at the heart of the MINC design. It doesn't hurt to be an expert, but you don't have to be one to do a large amount of constructive work with the system.

Record Keeping Aids. Part 2 contains a section (Mapping Data Transfer Connections) designed to assist you in the essential act of keeping records of what is connected to what in the applications you implement with MINC. You will soon discover that, as you develop more complex applications, clear and precise connection records are not only convenient, they are imperative.

# PART 1 DATA AQUISITION AND CONTROL

i

# CHAPTER 1 THE MINC DATA TRANSFER SYSTEM

Each MINC laboratory module (see Figure 1) consists of a metal-encased printed-circuit board with attached front panel and data transfer connector fingers along the top. These modules plug into a special MINC chassis which houses a power supply and a connector network. At the right end of the chassis, the connectors of this network accommodate processor-related modules not accessible to the user. Connectors in the central portion of the chassis accept up to eight MINC laboratory modules and are wired to make appropriate communications links with the processor when you plug a module into the chassis. The wiring also provides connections that permit modules to communicate with one another. A module can generate a signal for its own use or for use by neighboring modules. It can also use a signal originating in a neighboring module and pass it on to the next module or block further transmission. The result is an interconnection network defined by the particular modules plugged into the chassis at any given time.

The interconnections described above permit any given MINC module to communicate with its neighbor when plugged into any of the eight available chassis slots. However, placement of certain modules with respect to one another is restricted by a keying arrangement on the module front panels that prevents modules from being installed in ways that might cause component damage. In general, the analog-to-digital (A/D) converter, wherever it is located, becomes the focal point of most of the interconnection lines. These lines require that the dual multiplexers and preamplifiers be placed on the left of the A/D converter

MODULE PLACEMENT

for analog channel expansion. The interconnection lines also require that the digital to-analog (D/A) converter and the digital modules (clock, digital input, and digital output) be installed to the right of the A/D converter. Any unused slots in a finished configuration must occur to the left of the leftmost module; there can be no empty module slots to the right of any module. See Chapter 9, System Configuration Procedures, for more detail.

Figure 1. MINC Laboratory Module (A/D Converter)

# MINC FUNCTION DIAGRAMS

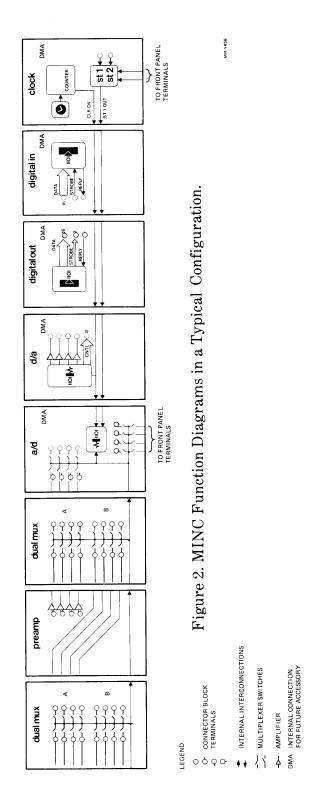

Each MINC module is provided with a top panel function diagram that symbolically represents the module's function and its principal interconnection lines to other modules. When modules are installed in the MINC chassis, these diagrams build a map of system functions and communications paths (see Figure 2).

Figure 2 shows the map created by the function diagrams on a typical system. Note that certain modules pass on signals that originate in neighboring modules. The digital input, digital output, and D/A converter, for example, pass clock signals to the A/D converter — and the preamplifier and multiplexer modules pass on signals from other modules situated to the left.

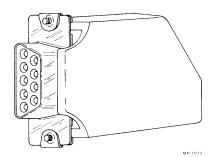

# MINC CONNECTOR BLOCKS

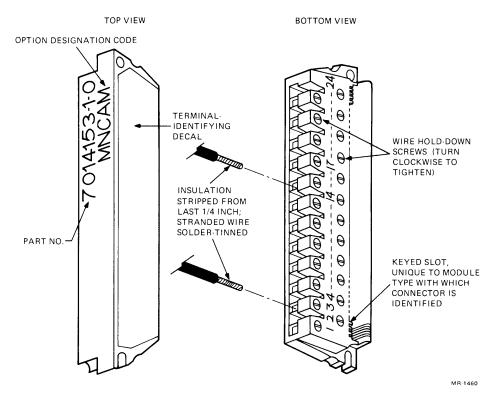

Except for the four single-ended channels accessed via the front-panel connectors on the A/D converter module, all MINC lab module connections can be made by means of the MINC connector blocks, illustrated in Figure 3.

Figure 3. MINC Connector Block

These connector blocks mate with the connector fingers accessible through the top of all MINC modules and permit up to 24 wires from external apparatus to be securely connected to those fingers. Wires are secured initially by means of the hold-down screws integral to the block. Once wires are installed, the connector can quickly be plugged onto the module and equally quickly replaced by a like connector associated with different apparatus. Note that connectors not only carry an identifying option designation code and a screw-terminal identifying label, but also are mechanically keyed to prevent an A/D connector, say, from being plugged onto a digital out or clock module. Connector blocks are identified by option designation codes, which are listed in Table 1. See Chapter 10, Connections to External Apparatus, for information about using MINC connector blocks.

#### MINC DATA TRANSFER SYSTEM

Table 1. MINC Module Option Designation Codes

| $Option\ Designation\ Code$ | Module              |

|-----------------------------|---------------------|

| MNCAD                       | A/D converter       |

| MNCAG                       | Preamplifier        |

| MNCAM                       | Dual multiplexer    |

| MNCKW                       | clock               |

| MNCAA                       | D/A converter       |

| MNCDI                       | Digital input unit  |

| MNCDO                       | Digital output unit |

i

#### CHAPTER 2 ANALOG-TO-DIGITAL CONVERSION

A/D conversions can involve up to four different kinds of MINC modules: the A/D converter itself, the preamplifier, the dual multiplexer, and the clock. These modules are referred to in this manual as the A/D group.

MINC A/D functions are invoked by the following BASIC routines (see *Book 6* for full details):

APPLICABLE LAB MODULE ROUTINES

AIN Collect analog input data

AIN\_HIST Generate frequency histogram using

analog input

AIN\_SUM Sum data from multiple analog sweeps

SET\_GAIN Set Preamplifier gain

TEST\_GAIN Check current gain and operating mode of

A/D channel

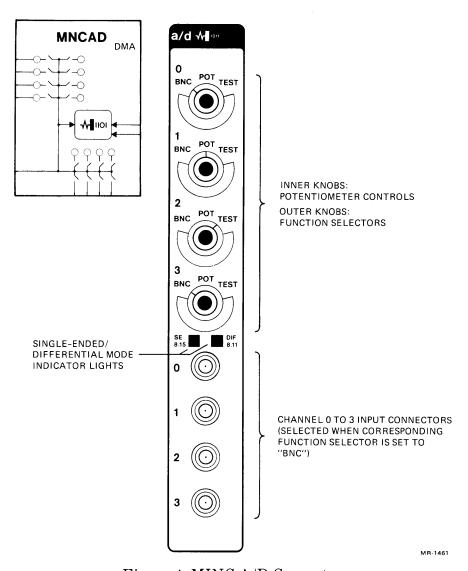

The MINC A/D converter (see Figure 4) is a successive approximation\* type analog-to-digital converter that translates the instantaneous value of a voltage applied to one of its inputs into a 12-bit binary value accessible to the system computer. The unit uses a patented auto-zeroing\* circuit that makes possible A/D conversions of unusually high stability and accuracy. It can operate in differential\* and/or single-ended\* mode and, through its own multiplexer, can accept data on as many as 16 channels. Assisted by MINC multiplexer modules, the A/D converter can accommodate up to 64 input channels. The unit's first four channels (0-3) receive their inputs via connectors on the front panel;

ANALOG-TO-DIGITAL CONVERTER the remaining inputs must be routed to the A/D connector block (see Figures 4 and 5).

Figure 4. MINC A/D Converter

Front Panel Controls. Four sets of dual concentric knobs on the front panel provide control of three input conditions for each channel from 0 through 3; knob 0 determines input to channel 0, 1 to 1, and so on. The outer knob of each pair has three positions:

BNC: selects as A/D input whatever signal is connected to the associated front-panel connector.

POT: selects as A/D input an internally supplied

reference that can be varied between -5.12 V

and +5.12 V by the inner control knob.

TEST: selects as A/D input one of four test conditions,

depending on the channel involved:

Channel 0: input connected to ground (0 volts)

Channel 1: input connected to an internally supplied 4.5 V level

Channel 2: input connected to an internally supplied -4.5 V level

Channel 3: input connected to an internally generated triangular wave with a frequency of approximately 9.5 Hz and an amplitude of approximately ±6 V.

These test signals provide definable input conditions that are useful in confirming proper operation of the A/D Converter. See Chapter 12.

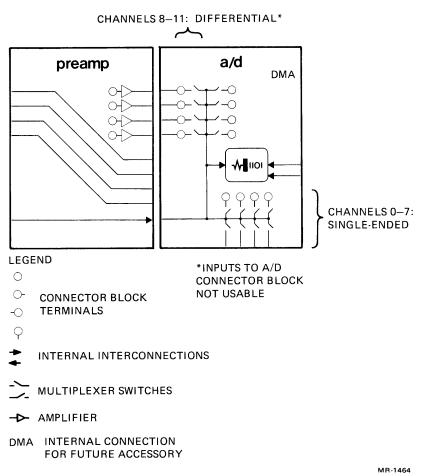

Mode Indicators. The MINC A/D accommodates two groups of inputs. The first group (lines 0-7, channels 0-7) always operates in single-ended\* (s.e.) mode. You can set the second group (by means of a ground connection to the s.e. terminal of the A/D connector block) to operate as eight single-ended channels (lines 8-15, channels 8-15). If the s.e. connection is absent or if a preamplifier occupies an adjacent slot to the left of the A/D converter, the second group operates as four differential\* channels (lines 8-15, channels 8-11). The mode indicator lights on the front panel visually identify which condition prevails for lines 8 to 15 at any time.

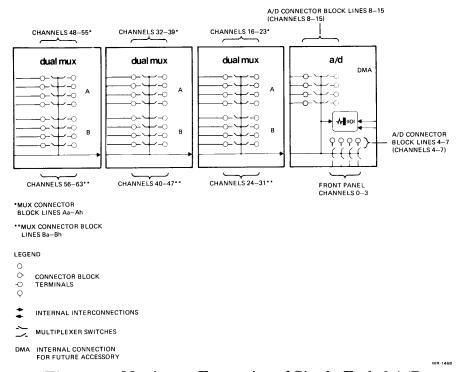

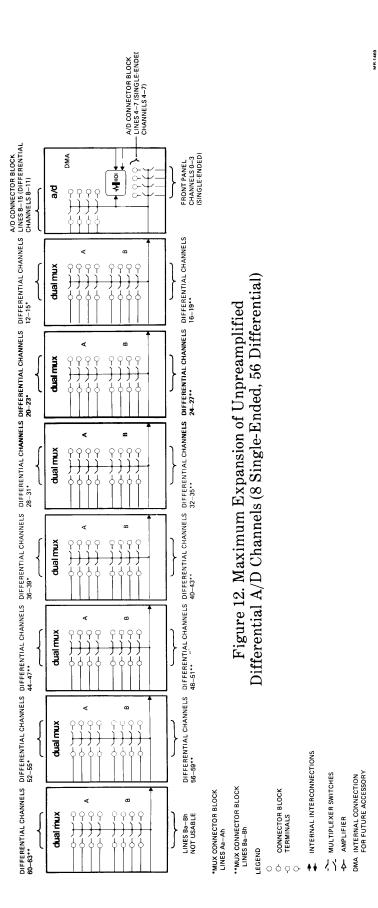

**Expansion**. The A/D converter is capable of supporting up to 64 single-ended or up to 56 differential and 8 single-ended input channels. Expansion beyond the 12 or 16 channels supported by the converter alone is accomplished by adding dual multiplexer modules to the left of the A/D converter (see The MINC Dual Multiplexer, below). The A/D communicates with and fully controls the multiplexers via prewired system interconnections.

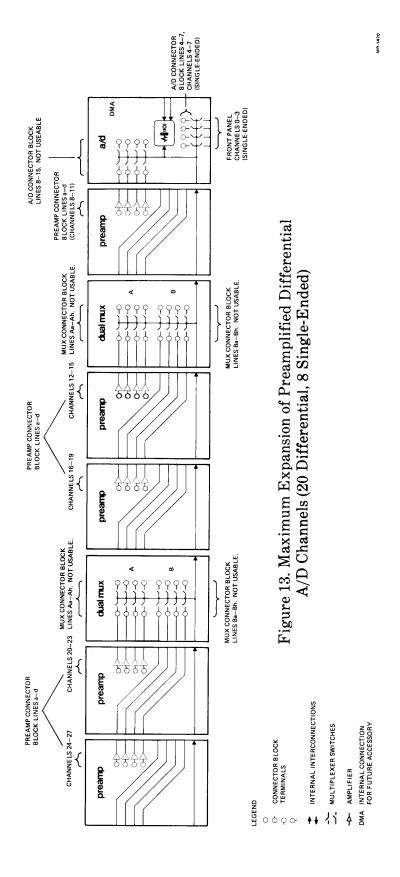

**Preamplified Inputs**. If you install a MINC preamplifier to the immediate left of the A/D or to the left of an associated multiplexer, input signals can be amplified by either manually selected or program-selected amounts. The preamplifier automatically identifies itself to the A/D, and the A/D automatically sets itself to differential operation for its second group of channels

whenever a conversion through the preamplifier is involved. If the preamplifier is to the immediate left of a multiplexer, the multiplexer automatically sets itself to differential operation for the affected group of channels. See The MINC Preamplifer, below.

**Initiation of A/D Conversions**. The A/D can initiate conversions immediately upon execution of a program statement, or in response to an external signal (see Book 6).

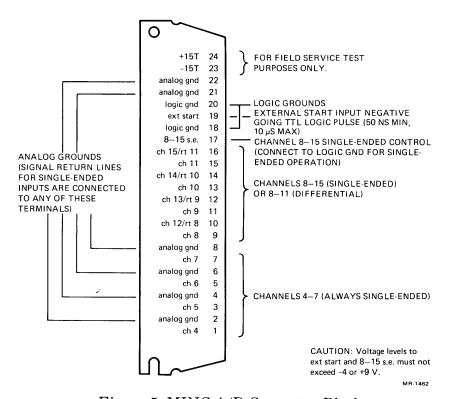

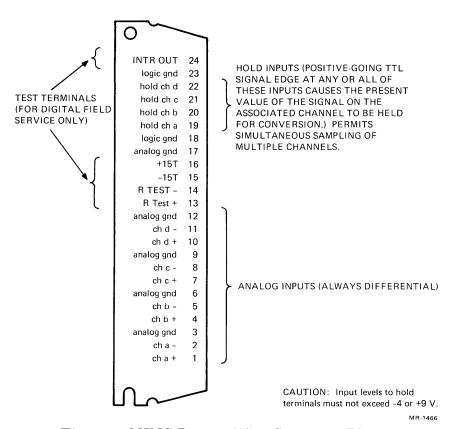

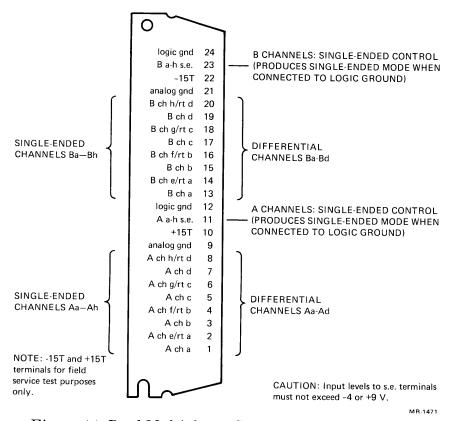

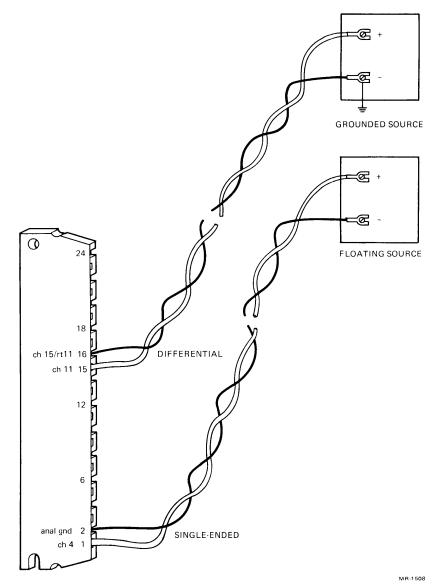

Connector Block Labeling. Two of the 24 terminals on the A/D connector block (15T and -15T) are test points that you can ignore. The remaining 22 terminals provide input and ground connections as defined in Figure 5. Note that certain terminals have dual identity — one for single-ended operation and one for differential operation. The terminal immediately above "ch 8," for example, is labeled "ch 12/rt8." If single-ended operation is selected ("8-15" s.e. connected to ground), this terminal is single-ended channel 12. If single-ended operation is not selected ("8-15" s.e. not connected to ground), this terminal is the differential return line for channel 8. And so it goes for the remaining dual-identity terminals on the A/D.

Figure 5. MINC A/D Connector Block

#### **PREAMPLIFIER**

The MINC preamplifier provides instrumentation-quality differential\* amplification or attenuation of signals on four input channels (see Figure 6). It permits gain to be controlled either by means of front panel knobs or by program argument, and it can be set to respond to resistance (kilohms) or current (milliamps) as well as voltage.

Figure 6. MINC Preamplifier

Front Panel Controls. The preamplifier front panel provides one set of dual concentric controls for each of the four channels. The inner knob in each set selects operating mode — voltage, current, or resistance. The outer knob selects the range for the chosen mode. Mode/range relationships are given in Table 2.

Table 2. Preamplifier Mode/Range Relationships

| Mode         |            | Gain                    |                       |                     |                     |

|--------------|------------|-------------------------|-----------------------|---------------------|---------------------|

|              |            | 500                     | 50                    | 5                   | 0.5                 |

| Voltage      | Setting    | ±0.01                   | ±0.1                  | ±1.0                | ±10                 |

| romgo        | Range (V)  | -0.01012 to<br>+0.01012 | -0.1012 to<br>+0.012  | -1.012 to<br>+1.012 | -10.12 to<br>+10.12 |

| Current      | Setting    | ±0.01                   | ±0.1                  | ±1.0                | ±10                 |

| current      | Range (mA) | -0.01012 to<br>+0.01012 | -0.1012 to<br>+0.1012 | -1.012 to<br>+1.012 | -10.12 to<br>+10.12 |

| Resistance   | Setting    | 0.1                     | 1.0                   | 10                  | 100                 |

| 100010101100 | Range (kΩ) | 0 to 0.1                | 0 to 1.0              | 0 to 10             | 0 to 100            |

The outer knob in each set is provided with a fifth position, P, which sets the preamplifier to a mode that permits the program to control gain. The knob must be in this position for the SET\_GAIN command to operate. See *Book 6* for more details.

Configuration with A/D or Multiplexer. The preamplifier is designed to communicate with an A/D converter or multiplexer situated to its immediate right. All necessary interconnections are made automatically when preamplifiers are installed in locations adjacent to dual multiplexers or A/Ds; no external connections between modules are required. When a preamplifier is installed to the immediate left of the A/D converter, the single-ended mode selection jumper, if installed, is defeated, and the preamplifier is automatically assigned to the differential four-channel group involving channels 8 through 11 (see Figure 7). Since the preamplifier now occupies channels 8-11, you can no longer use lines 8-15 on the A/D connector block. Doing so will interfere with proper transmission of preamplifier signals and may damage the equipment involved.

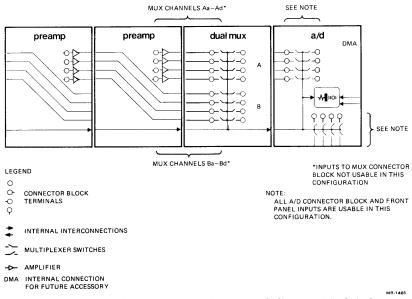

When a preamplifier is installed to the immediate left of a dual multiplexer, the preamplifier is assigned to the differential four-channel group involving multiplexer A, channels a through d. If two preamplifiers are so installed, they are assigned to the two contiguous differential four-channel groups provided by multiplexer A and multiplexer B (see Figure 8). Note that you cannot use dual multiplexer connector block lines Aa to Ah when one preamplifier is installed to the immediate left of a dual multiplexer. When two preamplifiers are installed to the immediate left of a dual multiplexer, you can use none of that multiplexer's connector block lines.

Channel codes and dual multiplexer/preamplifier configuration are further discussed under The MINC Dual Multiplexer, below.

Figure 7. Signal Routing — Preamplifier to A/D

Figure 8. Signal Routing — Preamplifier to Multiplexer

When a Preamplifier Is Required. The most obvious situation requiring a preamplifier is that in which output from a monitored instrument is too low for adequate resolution by the A/D converter. The A/D responds to levels as low as  $2.5 \, \text{mV}$ , but since it measures in  $2.5 \, \text{mV}$  increments, input levels must be at least  $50 \, \text{or} \, 100 \, \text{mV}$  if these quantum steps are not to introduce significant measurement errors. See Glossary, "Quantizing error."

Other situations requiring a preamplifier might include the following:

Changes in resistance or current (as from a temperature sensor, strain gauge, or photo-resistor) must be measured and input to the computer for storage or manipulation.

Output from a monitored instrument exceeds the  $\pm 5$  V range of the A/D and must be attenuated.

Output from a monitored instrument fluctuates widely and requires automatic gain setting (see SET\_GAIN command in *Book 6*).

Common mode\* rejection of the unpreamplified A/D converter is inadequate for the requirements of the application. In differential mode, A/D rejection of noise common to both differential inputs is very high for frequencies approaching DC, but diminishes as the frequency of that noise increases. The common-mode rejection of the preamplifier, however, is very high at all frequencies. (See Chapter 8 for further information.)

**Connector Block Labeling**. The MINC preamplifier connector block accommodates instrument connections as defined in Figure 9.

#### DUAL MULTIPLEXER

The MINC dual multiplexer (see Figure 10) consists of two multiplexers, A and B, each of which permits transfer of a program-selected analog signal on any of eight single-ended or four differential channels to a single transfer line on the MINC chassis connectors. From this point the selected signal travels via the chassis connector wiring and any intervening preamplifiers and multiplexers to the MINC A/D converter installed to the right. Each of the two multiplexers can be independently configured to operate as four differential\* or eight single-ended\* channels.

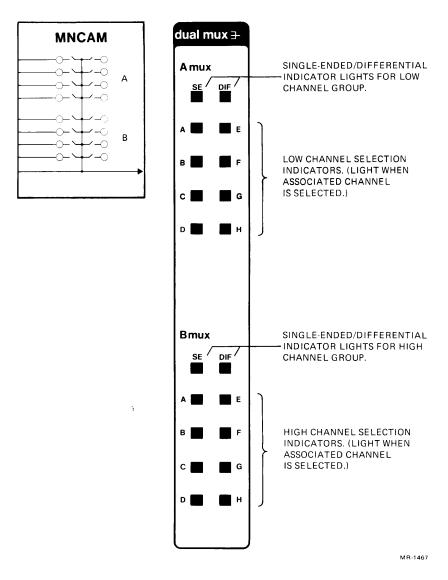

Front Panel Indicators. The dual multiplexer front panel contains 20 monitor lights that indicate which channel is currently

selected and which mode (single-ended or differential) the channel is set to.

Figure 9. MINC Preamplifier Connector Block

Configuration with A/D and Preamplifier. The dual multiplexer is designed to communicate with an A/D converter situated on its right, and with one or two preamplifiers situated on its immediate left. Both multiplexers and preamplifiers are designed to relay signals to the A/D converter from other multiplexers situated to the left. The result is that an A/D converter can be expanded to accommodate up to 64 single-ended or up to 56 differential plus 8 single-ended channels. Maximum expansions are illustrated in Figures 11, 12, and 13. Table 3 indicates the number of dual multiplexers required for any combination of single-ended and differential inputs.

When Multiplexers Are Required. A dual multiplexer is necessary whenever more A/D input channels are required than can be connected to the A/D converter alone. Remember that, although both the A/D converter and the multiplexer accommodate 16 input lines, the A/D requires that eight of these lines

(channels 0-7) always be single-ended. This means that only four differential channels can be accommodated on the lines that remain. Each dual multiplexer, however, can be configured when necessary to accommodate eight differential channels as well as four differential and eight single-ended. Note that MINC assigns channel numbers above 11 or 15 to inputs to dual multiplexers. This means that all inputs to the A/D connector block and front panel are available for connection to external signals even though one or more fully loaded multiplexers are installed in the system.

Figure 10. The MINC Dual Multiplexer

Figure 11. Maximum Expansion of Single-Ended A/D Channels

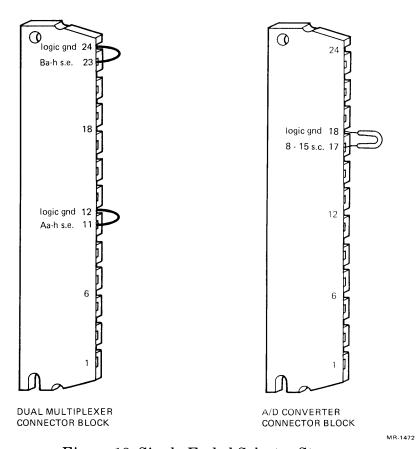

**Connector Block Labeling.** The multiplexer connector block accommodates 24 input, control, and ground connections to the multiplexer module. These connections are defined in Figure 14.

Channel identification on the multiplexer connector block, unlike that on the A/D connector block, is symbolic rather than literal. The reason is that the A/D connector block is always involved with the lowest 12 or 16 channels associated with any given MINC system, and numerical channel identification is therefore definable. The dual multiplexer, however, may be one of as many as seven such units on a system, and the numerical identity of its channels depends on how many channels have been accommodated by multiplexers and the A/D converter to its right. Here as elsewhere you will need to maintain accurate records of interface connections. See Chapter 10, Connections to External Apparatus.

#### NOTE

Channel identification by the A/D converter is dynamic and automatically takes into account whether

Table 3. Multiplexers Required to Support One A/D with n Differential and x Single-ended Input Channels

\*LAST MUX ONLY PARTIALLY ADDRESSABLE

or not channel groups are set for single-ended or differential operating mode. This means that if operating mode is changed for a low group of channels, the numbers of all channels above that group are automatically changed to accommodate the fact that four channels have in effect been inserted or withdrawn at the lower end.

Figure 14. Dual Multiplexer Connector Block Labeling

Assume, for example, that a system with 1 A/D and 1 multiplexer is configured to accommodate 8 single-ended channels (0-7) and 12 differential channels (8-19). Any program requesting conversions on the highest channel in the group would contain an argument specifying channel 19.

If channels 8-11 (on the A/D converter) were now to be converted to single-ended mode, they would thereby become channels 8-15. This change would automatically cause the 8 differential channels associated with the multiplexer to be assigned identification numbers from 16 to 23. If the program arguments were not al-

tered to accommodate these changes, all references to channels with numbers above 11 would be in error, and a call for a conversion on channel 19 would select the input previously associated with channel 15.

The simplest way of avoiding this confusion, and of precluding the need to rewrite large numbers of A/D statements, is to locate all analog inputs whose mode is subject to change at the high end of the channel sequence. If no channels exist that are higher than those whose mode has changed, then program arguments need be changed only for the changed channels. See also Random Channel Mode in *Book 6*.

#### **CLOCK MODULE**

To execute A/D conversions, not only must you identify appropriate channels and gain conditions, but you must also determine when and how often conversions are to occur. Lab module routines like AIN and AIN\_SUM (see *Book 6*) provide arguments that permit you to designate what events will be used to specify these conditions. Some of those arguments involve using the clock (see Chapter 3, Time Interval Control and Sampling), either as a time-base generator communicating with the A/D via the clock overflow line, or as a transducer of external events communicating with the A/D via Schmitt trigger 1.

**Configuration with A/D Converter.** The signal transfer paths of the module interconnection system permit a clock to communicate with an A/D converter anywhere to its left as long as no second clock and no A/D-group module intervenes. The D/A converter, the digital output, and the digital input all pass the clock signals to the left without intervention (see Figure 2).

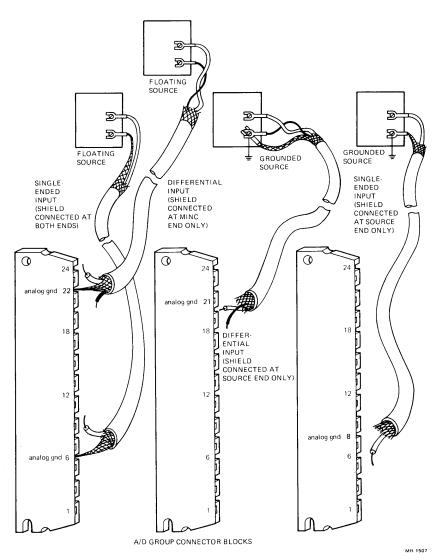

## ANALOG INPUT CONNECTIONS

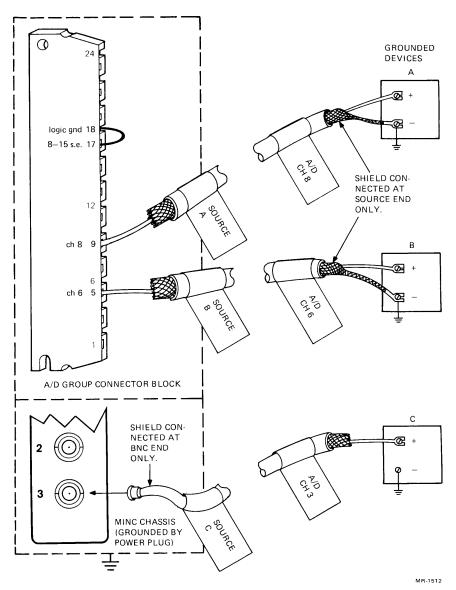

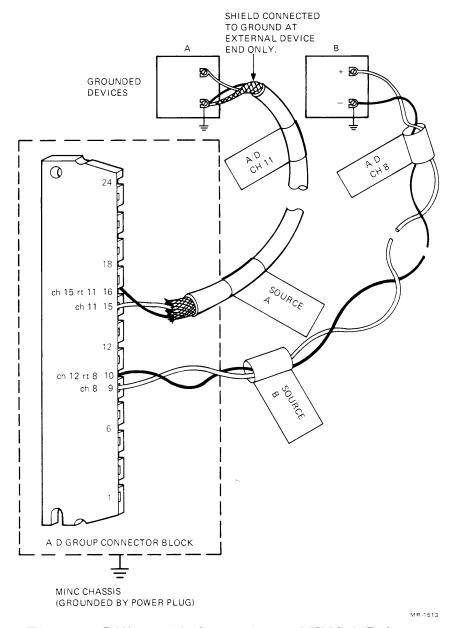

Connecting Grounded Apparatus. If the apparatus providing A/D input is grounded (that is, if its return terminal is connected to power line ground so that signal current can return thereby to the MINC System ground), make connections as illustrated in Figures 15 and 16. These figures show connections to the A/D connector block, but the principles illustrated apply equally well to preamplifier and multiplexer connections.

#### NOTE

It is good practice to label both ends of your lab module cables in a way similar to that suggested in the connection figures — that is, identifying at each end what is connected to the other. This facilitates confirmation of connections when installations grow complex.

Figure 15. Single-Ended\* Connections to MINC A/D Group from Grounded Sources

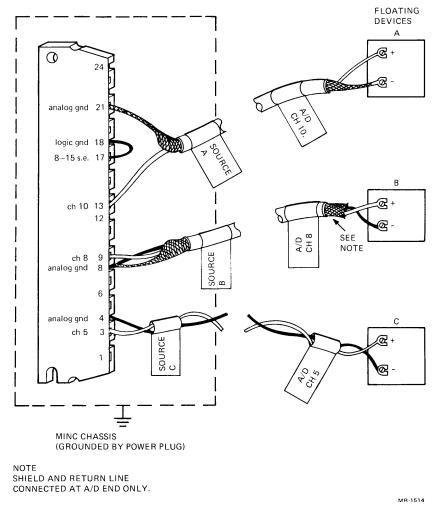

Connecting Floating Devices to the A/D Group. If the input device is floating (that is, if its return terminal is electrically isolated from power line ground as will be the case with most battery-operated, optically isolated, or transformer-coupled devices), make connections as illustrated in Figure 17. These figures show connections to the A/D connector block, but the prin-

ciples illustrated apply equally well to preamplifier and multiplexer connections. Note that the A/D requires a ground reference connection, even when operating in differential mode. Note also that there is no advantage to operating in differential mode when the signal source is floating.

Single-ended Selection Straps. You can set channels 8-15 of the A/D converter and both sections of the dual multiplexer to

Figure 16. Differential\* Connections to MINC A/D Group from Grounded Sources

operate in single-ended mode by installing connector block jumpers as illustrated in Figure 18.

Note that when you insert a preamplifier into a slot that communicates with a selected group of channels you cancel the effect of the single-ended selector straps. The preamplifier's presence is sensed by the A/D or multiplexer and conversions on the affected channels are made in differential mode whether or not the related single-ended strap is installed.

Figure 17. Single-Ended Connections to MINC A/D Group from Floating Sources

Input Selection (Channels 0-3). Input to channels 0-3 of the A/D is controlled by the larger of the two concentric knobs associated with each channel. To select signals connected to the associated front panel terminal set, the larger knob to the BNC posi-

tion. To select an internally generated DC voltage that can be varied throughout the A/D converter's range by the smaller inner knob, set the larger knob to POT. The TEST position selects a test input that is different for each of the first four channels. See the description at the beginning of this chapter.

Figure 18. Single-Ended Selector Straps

CONTROL SETTINGS AND CONNECTIONS Control settings and connections necessary to support A/D conversions in the MINC system are a function both of the program routines selected to implement the conversions and of the specific argument values chosen. Table 4 lists the routines that involve the A/D group and identifies those arguments that require specific front panel control settings or connector block connections. See *Book 6* for a full discussion of the listed routines.

$\begin{array}{c} \textbf{Table 4. Connections and Control Settings for} \\ \textbf{A/D Conversion Routines} \end{array}$

| Routine        | Argument       | Supporting User Action                                                              |

|----------------|----------------|-------------------------------------------------------------------------------------|

| AIN            |                |                                                                                     |

| (Collect       |                |                                                                                     |

| Analog Data)   |                |                                                                                     |

|                | mode ST2       | Connect desired device to clock ST2                                                 |

|                |                | input and select appropriate slope and                                              |

|                | mode X         | trigger conditions.  Connect external frequency source to                           |

|                | mode A         | clock ST1 and select appropriate slope                                              |

|                |                | and trigger conditions.                                                             |

|                | A/D-channel    | Insure that all specified analog input                                              |

|                | •              | channels are connected and that preamp                                              |

|                |                | gain/mode switches are properly set.                                                |

|                | rate=0         | Connect sampling trigger line to A/D                                                |

|                |                | ext start.                                                                          |

| $AIN_{HIST}$   |                |                                                                                     |

| (Analog        |                |                                                                                     |

| Histogram)     | A /TO 1 1      | T (1 (1 (1 (1 ) ) )                                                                 |

|                | A/D-channel    | Insure that the specified analog input channels are connected and the Preamp        |

|                |                | gain and mode switches are set as                                                   |

|                |                | desired.                                                                            |

| $SET\_GAIN$    | gain-code,     | Insure that each channel specified                                                  |

|                | A/D-channel    | is input to a preamplifier, and that the                                            |

|                |                | associated gain control is set as desired.                                          |

| AIN_SUM        |                | A/D                                                                                 |

| (Accumulate    |                | Connect apparatus specifying                                                        |

| Analog Sweeps) |                | start of sweep to clock ST2 input.                                                  |

|                | Mode=EXTERNAL  | Connect frequency source to clock ST1                                               |

|                | mono Birramina | input and select desired slope and                                                  |

|                |                | trigger conditions.                                                                 |

|                | rate=0         | Connect apparatus providing sampling                                                |

|                |                | trigger to clock ST1 input or to ext start                                          |

|                |                | input of A/D.                                                                       |

|                | A/D-channel    | Insure that each channel specified is                                               |

|                |                | input to a preamplifier, that the                                                   |

|                |                | associated gain control is set to "P", and that the mode control is set as desired. |

| ,              |                | that the mode control is set as desired.                                            |

i

# CHAPTER 3 TIME INTERVAL CONTROL AND SAMPLING

Many MINC control programs require time interval measurement and use one or another of two time-oriented mechanisms in the system. One of these is the system clock, which is present on all MINC systems and permits the computer to count line voltage cycles. Since power companies control line frequency with considerable precision, the system clock provides a precise time-base for some of the MINC routines. The SCHEDULE, PAUSE, and CIN routines use the system clock (see *Book 6*.)

All other time-dependent functions allowed by MINC program routines require one or two clock modules. These functions include not only the explicit elapsed-time and time-stamping routines (DIN, START\_TIME, GET\_TIME), but also those routines whose arguments specify sampling rate control, delays, or external timebase connections (for example, AIN, AOUT, DIN, DOUT, SCHMITT).

#### NOTE

If a system contains two clocks (clock 0 and clock 1), clock 0 must be to the left of clock 1. In such cases, clock-controlled data transfers and the SCHMITT routine use clock 0. The elapsed-time and time-stamping routines use clock 1. Clock 0 can be located anywhere to the left of clock 1 as long as it is not to the left of the A/D converter. Equipping a system with two clock modules permits simultaneous time measurement and clock- or Schmitt trigger-controlled data transfers. When a system contains only one clock, it is

### MINC TIME-KEEPING MODES

defined as clock 0 and requires that time-stamping and any routine invoking rate/delay parameters not be executed simultaneously. See Chapter 9 for information on configuring the second clock in a system.

Figure 19. The MINC Clock

#### MINC CLOCK

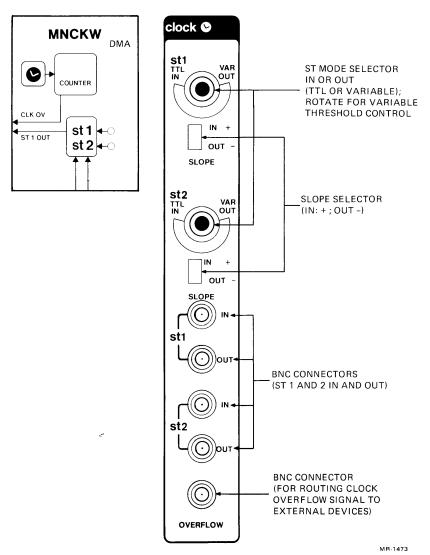

The MINC clock (see Figure 19) is a programmable counter that can be driven by a variety of events occurring either inside or outside the MINC system. Internal to the unit is a crystal-controlled oscillator that provides signals at 1 MHz, 100 kHz, 10 kHz, 1 kHz, and 100 Hz. The MINC routines select an appropriate frequency from among these to drive the counter. Also available as counter-drivers are the power line frequency and an

external input (ST1) that can accept regular or irregular rate signals. You can specify the line frequency and ST 1 inputs with lab module routine arguments (see *Book 6*).

Although for ease of use, the lab module routines conceal what actually happens from the user, these routines make use of the following attributes of the counter: 1) it can be read by the computer at any time; 2) it can be preset to any value within its range; and 3) it can signal the computer when it reaches its maximum count (overflows). The result is that under the control of the lab module routines, the computer/counter combination can identify the fact that any predetermined number of events has occurred. If these events have time significance, as in the case of the internally generated or power line frequencies, the unit becomes a clock. If the events do not have time significance — as in the case, say, of an organism response — the unit becomes an event totalizer or a predetermined counter.

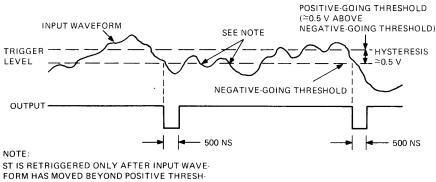

(A) SCHMITT TRIGGER OPERATION IN VARIABLE MODE (SLOPE SWITCH +)

FORM HAS MOVED BEYOND POSITIVE THRESH-OLD AND THEN AGAIN PASSED SELECTED NEGATIVE THRESHOLD.

(B) SCHMITT TRIGGER OPERATION IN VARIABLE MODE (SLOPE SWITCH -)

MR-1474

Figure 20. Schmitt Trigger Operation

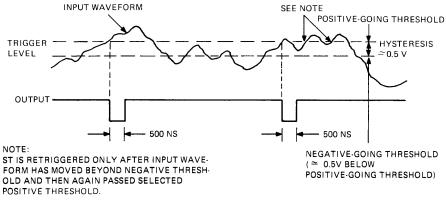

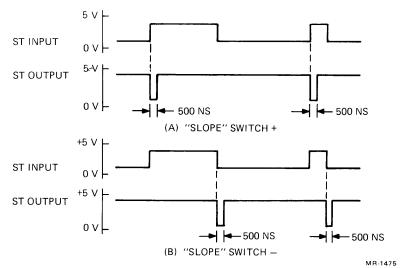

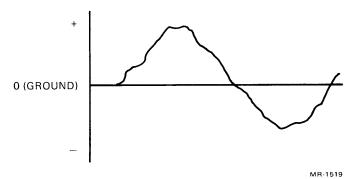

**Schmitt Triggers**. The clock module provides two Schmitt triggers (ST1 and ST2), which can work interactively with or independently of the clock itself. When arguments involve Schmitt trigger 1, both the SCHMITT and AIN routines can count Schmitt trigger operations and initiate actions when selected criteria have been met (see *Book 6*). Broadly defined, Schmitt triggers function to convert analog signals into digital signals—not by creating a digital equivalent of the analog value, as does the A/D converter, but by outputting a single negative-going digital pulse (TTL\* compatible) when a threshold value has been reached, as illustrated in Figure 20.

When the Schmitt trigger mode selector is set to VAR (variable mode), both the trigger threshold and the slope can be specified by front panel controls (see Figure 20). That is, each Schmitt trigger can be set to fire at a selected voltage point (controlled by the variable threshold knob) on either the positive-going or the negative-going slope of the waveform (controlled by the slope selector). In TTL mode (mode selector set to TTL), the trigger threshold is set automatically to a voltage point appropriate to integrated circuit logic levels and the SLOPE control determines whether firing will occur in response to a positive- or negative-going signal edge. Electrically, the only difference between Variable and TTL modes is that in the latter mode the threshold is fixed. See Figure 21.

Figure 21. Schmitt Trigger Operation in TTL Mode

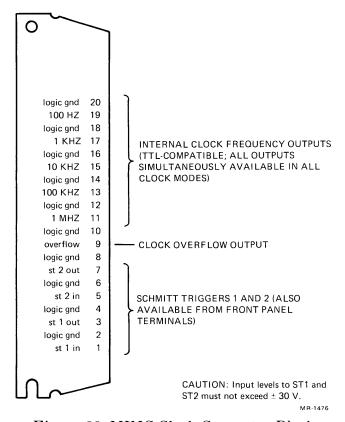

**The MINC Clock Connector Block**. Of the 20 connector block terminals, only terminals 1 to 8 are relevant for program control connections. The remaining terminals may be useful in complex applications, but no MINC routines either require or use them.

#### **CAUTION**

Alternate (and parallel) Schmitt trigger input and output terminals are provided both on the clock front panel and on the connector block. When connecting external apparatus to Schmitt trigger inputs or outputs, confirm that no connections have already been made on the alternate terminals. Failure to do so may result in damage to the external apparatus.

Figure 22. MINC Clock Connector Block

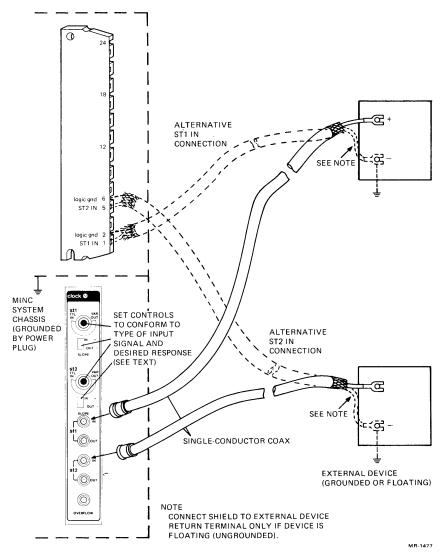

Control Settings and Connections. Most MINC routines use the clock in combination with other lab modules to control data transfer rates. The elapsed time routines, however, (START\_TIME and GET\_TIME) use the clock by itself to provide ongoing time-keeping capability with programmable resolution. No user connections are required for the elapsed time routines. The other lab module routines require connections to the clock only when the routine arguments invoke one or both of the clock's Schmitt triggers. Connections from external apparatus to Schmitt trigger inputs are made as illustrated in Figure 23.

Figure 23. MINC Clock — ST1 and ST2 Connections and Control

Tables 5 and 6 list the routines that can use clock Schmitt triggers and identify those arguments that require specific front-panel control settings or connector block connections. See Book 6 for a full discussion of the listed routines.

#### **CAUTION**

The clock Schmitt triggers can generate outputs in response to electrical noise when no device is connected to the input. To avoid such spurious responses from unused Schmitt triggers, set the mode selector to VAR

and turn the associated potentiometer to either of its extreme settings.

Table 5. Connections and Control Settings for MINC Clock Routines

| Routine                                               | Argument                     | Action Required                                                                                                                                                                                                    |

|-------------------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AIN<br>(Collect<br>Analog Data)                       | mode=ST2 mode=EXTERNAL       | Connect external signal source to clock ST2 input and select desired slope and threshold conditions. Connect external timebase source to clock ST1 input and select desired slope and threshold conditions.        |

|                                                       | rate=0                       | Connect apparatus providing sampling trigger to clock ST1 input or to A/D ext start input.                                                                                                                         |

| AIN_HIST<br>(Analog<br>Histogram)                     |                              | Connect apparatus providing sampling trigger to clock ST1 input or to A/D ext start input.                                                                                                                         |

| AIN_SUM<br>(Accumulate<br>Analog Sweeps)              | mode=EXTERNAL rate=0         | Connect external timebase source to ST1 input and select desired slope and threshold conditions. Connect apparatus providing sampling trigger to clock ST1 input or to A/D ext start input.                        |

| AOUT<br>(Send Analog<br>Data)                         | mode = ST2 $mode = EXTERNAL$ | Connect external start signal source to clock ST2 input and select desired slope and threshold conditions.  Connect external timebase source to clock ST1 input and select desired slope and threshold conditions. |

| DOUT<br>(Send Digital<br>Output)                      | mode=ST2                     | Connect external start signal to clock ST2 input and select desired slope and threshold conditions.                                                                                                                |

| Output                                                | mode = EXTERNAL              | Connect external timebase source to ST1 and select desired slope and threshold conditions.                                                                                                                         |

|                                                       | rate=0                       | Connect external apparatus reply line to DO reply terminal.                                                                                                                                                        |

| PST_HIST<br>(Generate Post-<br>Stimulus<br>Histogram) |                              | Connect source producing a signal at stimulus time to clock ST1; connect source producing a signal at response time to clock ST2. Set slope and threshold conditions as appropriate.                               |

| SCHMITT<br>(Respond to<br>Schmitt Trigger<br>Input)   | trigger=1                    | Connect source of signals that must elicit program responses to ST1 input and select desired slope and threshold conditions.                                                                                       |

| . /                                                   | trigger=2                    | Connect external start signal to clock ST2 input and select desired slope and threshold conditions.                                                                                                                |

| TIME_HIST<br>(Generate Time<br>Interval<br>Histogram) |                              | Connect source of signals whose intervals are to be measured to clock ST2 input and select desired slope and threshold conditions.                                                                                 |

| DIN<br>(Collect<br>Digital Input)             | mode=EXTERNAL | Connect external timebase source to clock ST1 input and select desired slope and threshold conditions.                                                             |

|-----------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Digital Input)                                | mode=ST2      | Connect external signal source to clock ST2 input and select desired slope and threshold conditions.                                                               |

|                                               | rate=0        | Connect external apparatus generating sampling trigger to DI strobe (HB or LB STRB) terminal. For independent event sampling connect apparatus to D00 through D15. |

| START_TIME<br>(Start Elapsed<br>Time Counter) | mode=EXTERNAL | Connect external timebase source to clock ST1 input and select desired slope and threshold conditions.                                                             |

| ,                                             | mode=ST2      | Connect external start signal to clock ST2 input and select desired slope and threshold conditions.                                                                |

Table 6. Connections and Control Settings for Timestamping and Elapsed Time Routines

| Routine                | Argument       | Action Required                                                                                                                                                                                              |

|------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIN 4                  | mode=TIMESTAMP | Insure either that Clock 1 is installed in addition to Clock 0 or that no other routine invokes Clock 0 while DIN is executing.                                                                              |

|                        | mode=ST2       | (See Note) Connect drive specifying DIN start to ST1 input and select desired slope and threshold conditions. (If mode ST2 and TIMESTAMP are invoked in the same routine, Clock 1 <i>must</i> be installed.) |

|                        | mode=EXTERNAL  | Connect external frequency source to ST1 input and select desired slope and threshold conditions. (If EXTERNAL mode and TIMESTAMP are invoked in the same routine, Clock 1 <i>must</i> be installed.)        |

| START_TIME<br>GET_TIME |                | Insure either that Clock 1 is installed or that no other routine invokes Clock 0 during execution of timestamping command(s).                                                                                |

Note: The timestamp clock/elapsed time counter functions only in programmed mode; it will be stopped upon entry into immediate mode, and an error message will indicate that it has been running.

# CHAPTER 4 DIGITAL-TO-ANALOG CONVERSION

Applicable program command:

AOUT (Send Analog Data)

See Book 6 for complete description.

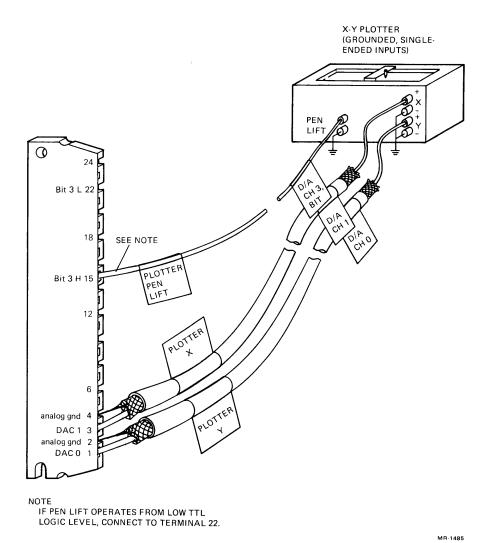

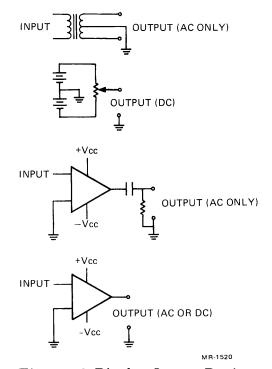

The MINC digital-to-analog (D/A) converter (see Figure 24) is a module housing four independent D/A converters (DACs), each of which is defined as a channel by the AOUT routine. The module receives numeric values from a program, preserves them in holding registers for each channel, and converts them to equivalent voltages at the associated output terminals. These voltages are sustained without further user involvement until new values arrive for those channels. The four DACs in the module accept data from the system via internal 12-bit binary registers. All DACs are therefore capable of a resolution of one part in 4096. Each DAC is provided with mode/range controls that permit user selection of unipolar\* or bipolar\* operation with a variety of output ranges (see D/A Input/Output Relationships, below).

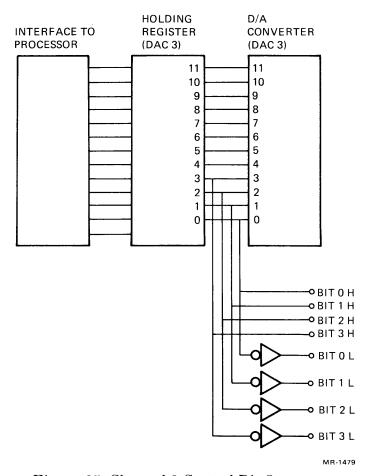

All four DACs on each module are identical except for DAC 3, which routes the 4 least significant bits of its binary-encoded holding register to 8 user-accessible output terminals (4 normal and 4 inverted), as well as to the DAC 3 digital-to-analog converter circuit (see Figure 25). The result is that you can specify digital data to DAC 3 that will not only produce the desired analog output voltage but will also provide such control information as *intensify* (to storage oscilloscopes) or *raise pen* (to X-Y plotters). Forcing these bits to values other than those required

#### DIGITAL-TO-ANALOG CONVERTER

by the conversion will affect conversion accuracy. However, these are the least significant four bits in the 12-bit data word that specifies the analog output voltage. They can therefore affect the DAC 3 output by less than 1% of its full-scale range.

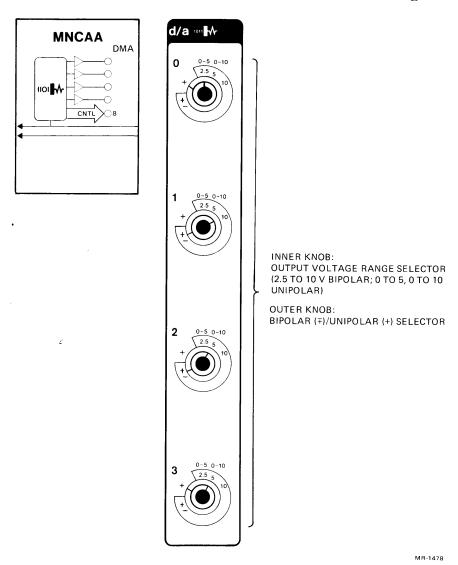

Figure 24. The MINC D/A Converter

D/A Input/Output Relationships. Two concentric knobs (see Figure 24) associated with each of the four channels on the MINC D/A converter permit you to select mode and range. Mode settings are unipolar (+) and bipolar (±); range settings are as follows:

Unipolar: 0-5 (0 to +5.11875 Volts)

0-10 (0 to +10.2375 Volts)

Bipolar: #2.5 (-2.56 to +2.55875 Volts) #5 (-5.12 to +5.1175 Volts) #10 (-10.24 to +10.235 Volts)

Figure 25. Channel 3 Control Bit Outputs

The AOUT routine (see *Book 6*) allows data in the range of -2048 to 2047. Because the condition of the control switches is not sensed by the system, it is up to you to set switches in a way that is consistent with your input data on the one hand and the device that receives the analog output voltage on the other. The relationship between data values made available to AOUT and voltages actually output is illustrated in Table 7.

Minimum Voltage Increments. If we exclude 0, the total number of distinct AOUT data values is 4095 (-2048 to 2047). This is so because 4095 is the largest number that can be represented by the 12-bit binary circuits that perform the conversions. Since these are integer values, the smallest change we can make on any DAC output voltage is that created by adding or subtracting

1 from the data value which generated that voltage. Conversely, the way to calculate what output voltage a DAC will produce in response to a given data value is to multiply the data value by the value of the smallest change, or minimum voltage increment.

| Table 7. | $MINC \Gamma$ | / A   | Data/  | Voltage    | Relationships |

|----------|---------------|-------|--------|------------|---------------|

| TWOIC II | 111110        | / * * | D a ca | 1 OI UUS C | rectations    |

| Input Value | OUTPUT (Bipolar) |         | OUTPUT (Unipolar) |              |               |

|-------------|------------------|---------|-------------------|--------------|---------------|

| Input value | ±2.56V           | ±5.12V  | -10.24V           | 0V to +5.12V | 0V to +10.24V |

| -2048       | -2.56            | -5.12   | -10.24            | +0.0         | +0.0          |

| -2047       | -2.55875         | -5.1175 | -10.235           | +0.00125     | +0.025        |

| -0001       | -0.00125         | -0.0025 | - 0.005           | +2.55875     | +5.1175       |

| 0000        | -0.0             | -0.0    | - 0.0             | +2.56        | +5.12         |

| +0001       | +0.00125         | +0.0025 | + 0.005           | +2.56125     | +5.1225       |

| +2047       | +2.55875         | +5.1175 | +10.235           | +5.11875     | +10.2375      |

Table 8 shows the minimum voltage increments associated with all MINC D/A modes and ranges. Notice that multiplying these values by -2048 and 2047 produces the full range values for bipolar operation given in Table 7. Multiplying these values by 4095 produces the full range values for unipolar operation given in Table 7.

Table 8. Minimum D/A Voltage Increments

| Mode     | Range | Minimum            | Increments |

|----------|-------|--------------------|------------|

| Unipolar | 0-10  | .0025V             | (2.5mV)    |

| (+)      | 0-5   | .00125V            | (1.25mV)   |

| Bipolar  | 10    | .005V              | (5mV)      |

| (Ŧ)      | 5     | .0025V             | (2.5mV)    |

|          | 2.5   | $.00125\mathrm{V}$ | (1.25 mV)  |

To derive a data value that will produce a desired voltage under a given range condition, use one of the two equations below:

> Unipolar: D = V/M - 2048 (PRINT V/M - 2048) Bipolar: D = V/M (PRINT V/M)

where D is an integer between -2048 and 2047, V is expressed in volts, and M is the minimum increment (in volts) associated with the selected range as given in Table 8.

**Expansion**. The MINC system supports up to four D/A converter modules (16 channels), provided that the address and vector switches are configured as indicated on the label affixed to the side of each module (see also Chapter 9, System Configuration Procedures). If only one MINC D/A converter exists in a

system, it should be configured as unit 0. Subsequent units should be configured sequentially up to 3. No omissions can be tolerated in the sequence. If three D/A modules are configured as units 0,2, and 3, the system will not be able to detect the presence of units 2 and 3. If two units are configured as units 1 and 2, the system will permit no D/A conversion because it will detect no D/A modules.

From the point of view of the AOUT routine, channels are numbered sequentially from 0 to 15 (maximum), channels 0-3 occupying unit 0, 4-7 occupying unit 1, and so forth.

Figure 26. MINC D/A Connector Block

**DAC 3 Resolution**. The fourth DAC on each module (that is, channels 3, 7, 11, and 15 on systems with four D/A modules), provides user access to the four least significant bits of the holding register as described above. If these bits are unused on channels 7, 11, or 15, D/A conversions can be made with full accuracy. On channel 3, however, bit 0 is regularly used by the AOUT routine to specify intensify time to a possible oscilloscope. Its state is therefore unpredictable even when you are using none of the control bits on channel 3. This reduces the resolution of channel

3 to two parts in 4096 rather than one in 4096. Note that the full-scale accuracy of channel 3 is virtually unaffected by the indeterminate character of bit 0. Bit 0's uncertainty adds 1 minimum voltage increment (see Table 8) to the uncertainty of any channel 3 conversion. This amounts to less than .025% of any full-scale conversion.

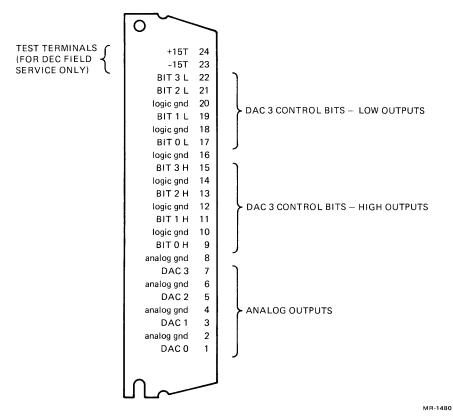

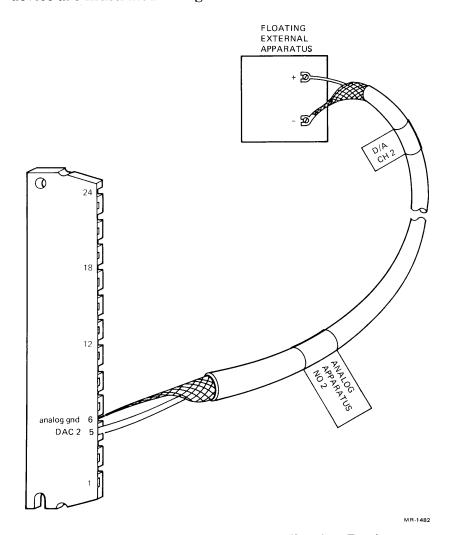

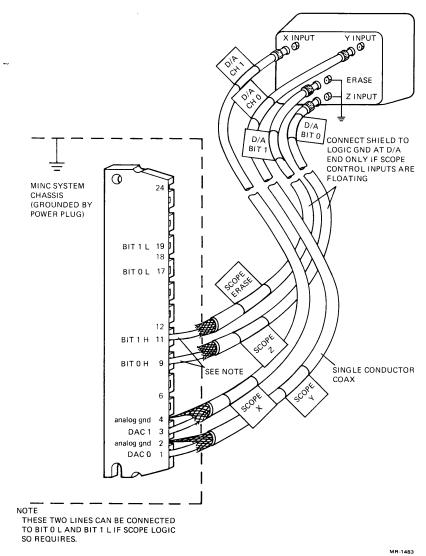

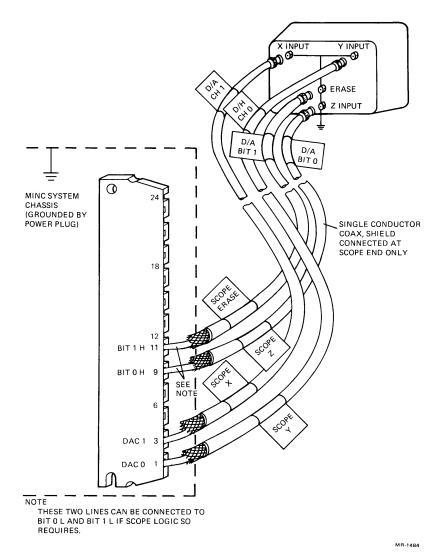

**Connector Block.** The MINC D/A connector block, shown in Figure 26, provides terminals for connecting external apparatus to all four analog output channels (DAC 0 to DAC 3) and their grounds (analog gnd). Note that terminals for bits 0 to 3 allow you to choose between a high logic level\* when the bit in

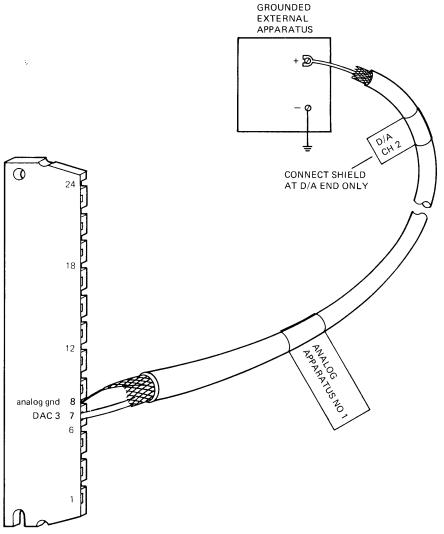

Figure 27. D/A Connections to a Grounded Device

question is set ("Bit n H") and a low logic level when that bit is set ("Bit n L"). This choice exists because some oscilloscopes and plotters require a high logic level to execute such functions as "intensify" and "raise pen," while others require a low logic level. Terminals 23 and 24 are test points for Digital Field Service personnel.